错误 #1751

【系统卡顿问题】T5版本上行2天线星创易联cpe接入后phy必挂死,四信cpe接入灌包后偶尔出现phy挂死

开始日期:

2024-04-28

计划完成日期:

% 完成:

0%

预期时间:

问题归属:

DRV, PHY

发现问题版本:

Rel_2.1.14P

目标解决问题版本:

Rel_2.1.14P

FPGA板卡类型:

115P+PRU

CPU类型:

Xeon-gold5218(宝德)

描述

【环境信息】:核心网(Rel_3.1.0)+bbu(宝德服务器、2.1.14P-pre2T5版本)+pru(3.5G)+yzmm(YZMM2.1.0(qh))

【参数配置】:上行2天线

【问题描述】:在2.1.14p_pre2T5版本上,大上行子帧配置下,上行2天线星创易联cpe接入后phy必挂死,四信cpe接入灌包后偶尔出现phy挂死;

【问题频率】:必现

【问题影响】:产品功能

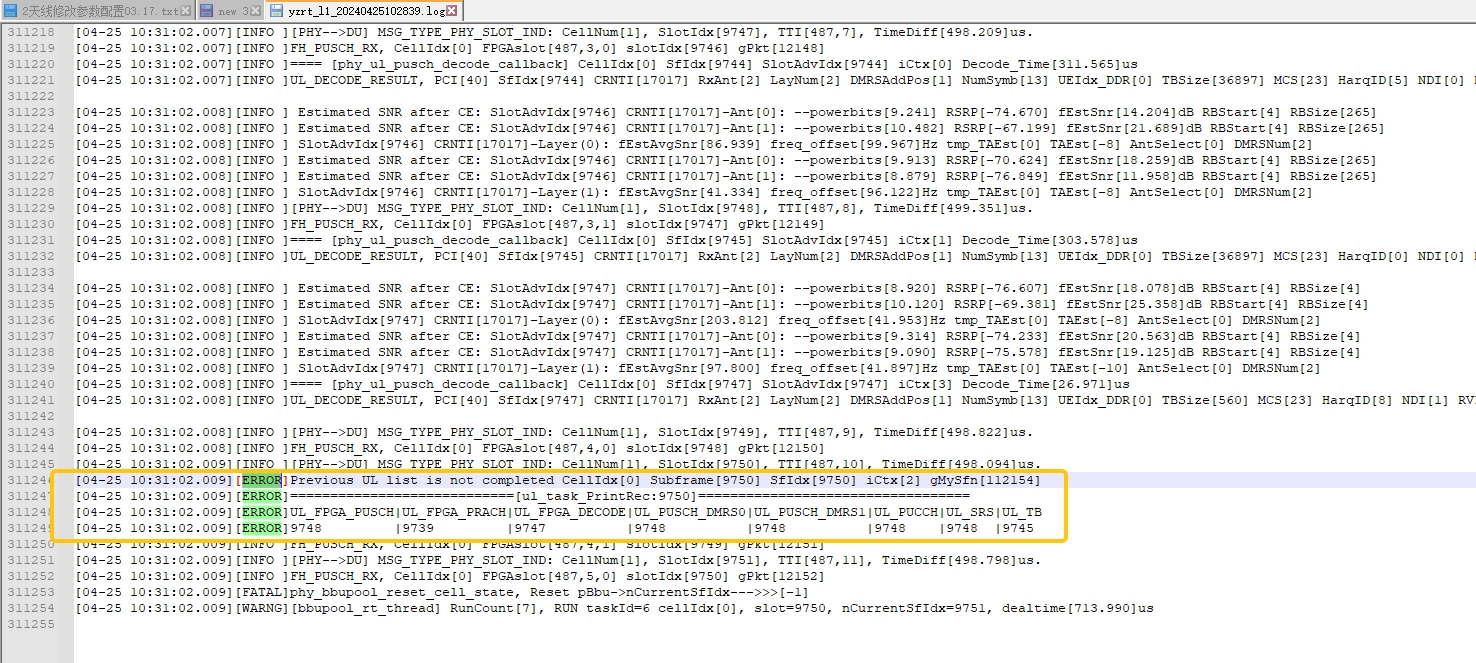

【问题分析】:分析phy日志,怀疑为上行任务超时,需要phy层进一步分析定位;

文件

相关的问题

历史记录

由 匿名用户 更新于 将近 2 年 之前

- 状态 从 新建 变更为 进行中

修改增加调测的版本,发现 phy在ul post 任务后的后处理函数 存在被阻塞的情况如下:

[04-26 14:09:21.928][DEBUG]---- 6_UL_L1_CONFIG, CellIdx[0] Subframe[4127] SlotAdvIdx[4127] iCtx[3] TimeDiff[501.958]us

[04-26 14:09:21.928][DEBUG][Begin]=======================[UL_Format0_CONFIG][RX:206,7]============================

[04-26 14:09:21.928][DEBUG]UEId|nRNTI|StartPRB|StartPRB2ndHop|StartSym|SymNum|FreqHop|GroupHop|SeqHop|HopId|m0 |SrCheck|Payload|RxAnt|nSlot

[04-26 14:09:21.928][DEBUG]0 |17017|8 |0 |13 |1 |0 |0 |0 |40 |0 |0 |1 |2 |7

[04-26 14:09:21.928][DEBUG]UL_CONFIG_STAT_COUNT: NumPUSCH[0] NumPUCCH[1] NumSRS[0] Ack[0] PuschTwoSlotProc[0] PUCCHFormat(0-4)[1, 0, 0, 0, 0]

[04-26 14:09:21.928][DEBUG]PUSH_API_TO_QUEUE:[push:44, pop:43], apiArraySfn[4130] numInQueue[25]

[04-26 14:09:21.928][DEBUG]phy_ul_pusch_symbol_buffer_pre_alloc_func, RX[206, 7], PUSCHGrantNum[0]

[04-26 14:09:21.928][ERROR]taskInnerScheduler:readSf[4087] taskSlot[4127] nRow[7] taskType[17], queueId[0] cell[0] prefer_cell[16] readOffset[0] writeOffset[1] nThreadIdx[4]

[04-26 14:09:21.928][ERROR]taskInnerScheduler, fixed TaskSlot[4127] --->pnReadSf[4087]!!

[04-26 14:09:21.928][DEBUG][phy_dl_x86_encode_task_func]: CellIdx[0] SlotIdx[4127] SlotAdvIdx[4129] Ctx[1] FEC_DealTime[0.108]us

[04-26 14:09:21.928][ERROR]!!![bbupool_rt_thread] DEADLINE taskId=17 cellIdx=0 slot=4087 nCurrentSfIdx=4127, nSfDiff[-40], processingTimeOffset[-5]

[04-26 14:09:21.928][DEBUG]Func:Reset_ul_buf, CellIdx[0] slot[4087] SlotAdvIdx[4087] iCtx[3] PhyState[1] bufIdx[2] RBNum[273] oneSymDataSize[13104] // 4087的后处理函数被阻塞,在40个slot后才触发。

[04-26 14:09:21.928][INFO ]FH_PUSCH_RX, CellIdx[0] FPGAslot[206,3,0] slotIdx[4126] gPkt[4928]

修改版本 YZS_PRU_V2.0.120_20240428 测试中。