错误 #2660

【2.1.16P_pre1T1】coreset1配成2个symbol,上行误码率达到70%

0%

描述

基站配置大上行,coreset1配置成2个symbol

E500模拟1个UE,接入后灌上下行包,PHY窗口显示的误码率到70%,上行MCS降为0。

在L1 log里看到在slot3-7,PUSCH功率检测不到,

[01-07 12:00:56.631][INFO ] Estimated SNR after CE: SlotAdvIdx10635 CRNTI17017-Ant0: --powerbits[5.320] RSRP[-98.278] fEstSnr[-7.024]dB RBStart4 RBSize265

[01-07 12:00:56.631][INFO ] Estimated SNR after CE: SlotAdvIdx10636 CRNTI17017-Ant0: --powerbits[5.308] RSRP[-98.351] fEstSnr[-6.351]dB RBStart4 RBSize251

[01-07 12:00:56.632][INFO ] Estimated SNR after CE: SlotAdvIdx10637 CRNTI17017-Ant0: --powerbits[5.342] RSRP[-98.148] fEstSnr[-6.897]dB RBStart4 RBSize265

[01-07 12:00:56.632][INFO ] Estimated SNR after CE: SlotAdvIdx10638 CRNTI17017-Ant0: --powerbits[8.853] RSRP[-77.011] fEstSnr[18.210]dB RBStart4 RBSize265

[01-07 12:00:56.633][INFO ] Estimated SNR after CE: SlotAdvIdx10639 CRNTI17017-Ant0: --powerbits[8.816] RSRP[-77.230] fEstSnr[18.252]dB RBStart18 RBSize251

[01-07 12:00:56.634][INFO ] Estimated SNR after CE: SlotAdvIdx10643 CRNTI17017-Ant0: --powerbits[5.309] RSRP[-98.345] fEstSnr[-6.547]dB RBStart4 RBSize265

[01-07 12:00:56.635][INFO ] Estimated SNR after CE: SlotAdvIdx10644 CRNTI17017-Ant0: --powerbits[5.314] RSRP[-98.317] fEstSnr[-6.941]dB RBStart4 RBSize265

[01-07 12:00:56.636][INFO ] Estimated SNR after CE: SlotAdvIdx10645 CRNTI17017-Ant0: --powerbits[5.321] RSRP[-98.273] fEstSnr[-7.009]dB RBStart4 RBSize265

[01-07 12:00:56.636][INFO ] Estimated SNR after CE: SlotAdvIdx10646 CRNTI17017-Ant0: --powerbits[5.333] RSRP[-98.203] fEstSnr[-6.487]dB RBStart4 RBSize265

[01-07 12:00:56.637][INFO ] Estimated SNR after CE: SlotAdvIdx10647 CRNTI17017-Ant0: --powerbits[5.323] RSRP[-98.262] fEstSnr[-6.589]dB RBStart4 RBSize265

[01-07 12:00:56.637][INFO ] Estimated SNR after CE: SlotAdvIdx10648 CRNTI17017-Ant0: --powerbits[8.648] RSRP[-78.244] fEstSnr[17.843]dB RBStart4 RBSize265

[01-07 12:00:56.638][INFO ] Estimated SNR after CE: SlotAdvIdx10649 CRNTI17017-Ant0: --powerbits[8.501] RSRP[-79.128] fEstSnr[15.986]dB RBStart4 RBSize265

[01-07 12:00:56.640][INFO ] Estimated SNR after CE: SlotAdvIdx10653 CRNTI17017-Ant0: --powerbits[5.306] RSRP[-98.364] fEstSnr[-6.356]dB RBStart4 RBSize265

[01-07 12:00:56.640][INFO ] Estimated SNR after CE: SlotAdvIdx10654 CRNTI17017-Ant0: --powerbits[5.302] RSRP[-98.387] fEstSnr[-6.670]dB RBStart4 RBSize265

[01-07 12:00:56.641][INFO ] Estimated SNR after CE: SlotAdvIdx10655 CRNTI17017-Ant0: --powerbits[5.327] RSRP[-98.237] fEstSnr[-6.551]dB RBStart4 RBSize265

[01-07 12:00:56.641][INFO ] Estimated SNR after CE: SlotAdvIdx10656 CRNTI17017-Ant0: --powerbits[5.299] RSRP[-98.406] fEstSnr[-6.578]dB RBStart4 RBSize251

[01-07 12:00:56.642][INFO ] Estimated SNR after CE: SlotAdvIdx10657 CRNTI17017-Ant0: --powerbits[5.300] RSRP[-98.401] fEstSnr[-6.820]dB RBStart4 RBSize265

[01-07 12:00:56.642][INFO ] Estimated SNR after CE: SlotAdvIdx10658 CRNTI17017-Ant0: --powerbits[8.725] RSRP[-77.776] fEstSnr[18.059]dB RBStart4 RBSize265

[01-07 12:00:56.643][INFO ] Estimated SNR after CE: SlotAdvIdx10659 CRNTI17017-Ant0: --powerbits[8.743] RSRP[-77.670] fEstSnr[17.653]dB RBStart18 RBSize251

[01-07 12:00:56.645][INFO ] Estimated SNR after CE: SlotAdvIdx10663 CRNTI17017-Ant0: --powerbits[5.303] RSRP[-98.380] fEstSnr[-6.631]dB RBStart4 RBSize265

[01-07 12:00:56.645][INFO ] Estimated SNR after CE: SlotAdvIdx10664 CRNTI17017-Ant0: --powerbits[5.291] RSRP[-98.451] fEstSnr[-6.729]dB RBStart4 RBSize265

[01-07 12:00:56.646][INFO ] Estimated SNR after CE: SlotAdvIdx10665 CRNTI17017-Ant0: --powerbits[5.295] RSRP[-98.427] fEstSnr[-6.399]dB RBStart4 RBSize265

[01-07 12:00:56.646][INFO ] Estimated SNR after CE: SlotAdvIdx10666 CRNTI17017-Ant0: --powerbits[5.304] RSRP[-98.377] fEstSnr[-6.871]dB RBStart4 RBSize265

[01-07 12:00:56.647][INFO ] Estimated SNR after CE: SlotAdvIdx10667 CRNTI17017-Ant0: --powerbits[5.319] RSRP[-98.285] fEstSnr[-6.690]dB RBStart4 RBSize265

[01-07 12:00:56.647][INFO ] Estimated SNR after CE: SlotAdvIdx10668 CRNTI17017-Ant0: --powerbits[8.649] RSRP[-78.237] fEstSnr[18.091]dB RBStart4 RBSize265

文件

历史记录

由 匿名用户 更新于 大约一年 之前

- 文件 MZTD2NfGOx.jpg MZTD2NfGOx.jpg 已添加

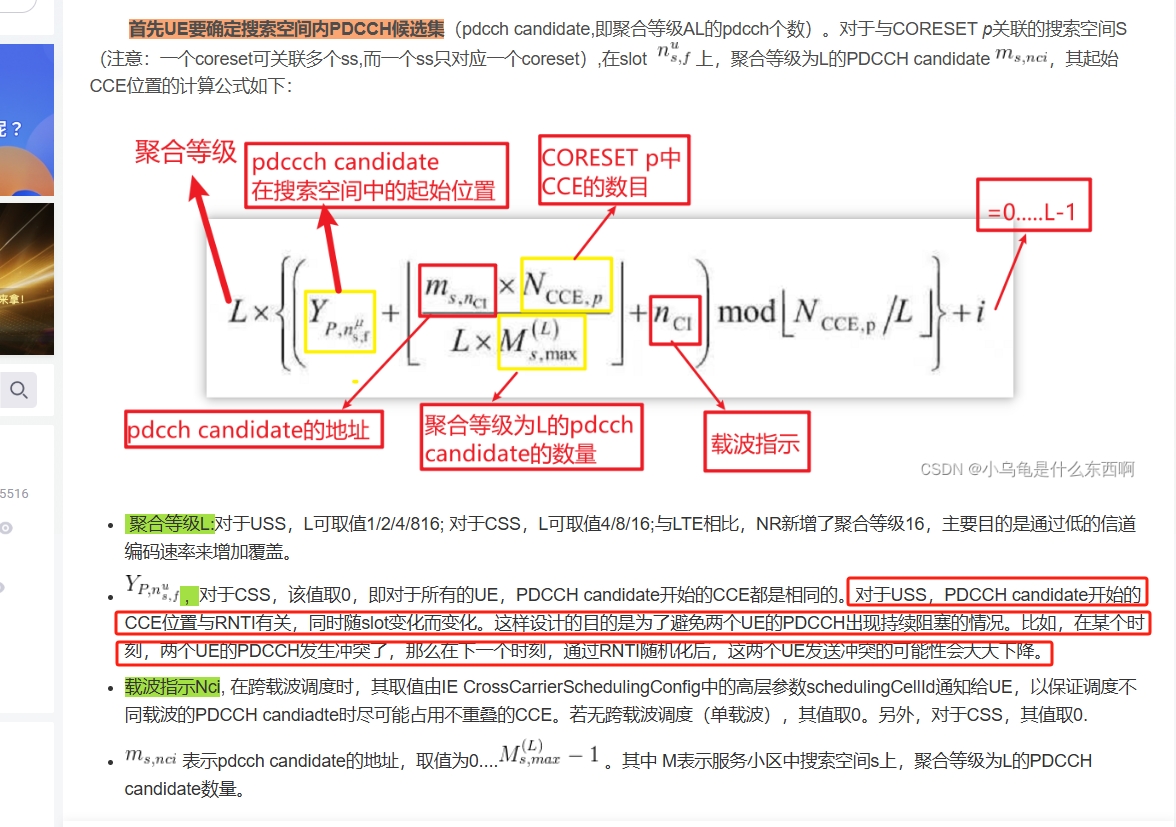

CORESET1配置2symbol测试:

添加日志后发现同一个slot上分配的CCE存在重叠,从而导致UE解不对PDCCH,进一步导致了高误码的问题;

走读代码发现CCE的分配方式存在问题,从而导致,CCE重复分配的情况;

修改后,E500上高误码问题未出现。

但是2symbol的情况下仍然存在pdcch资源分配失败的情况,待进一步定位

由 匿名用户 更新于 大约一年 之前

- 文件 qW4Tmery6z.jpg qW4Tmery6z.jpg 已添加

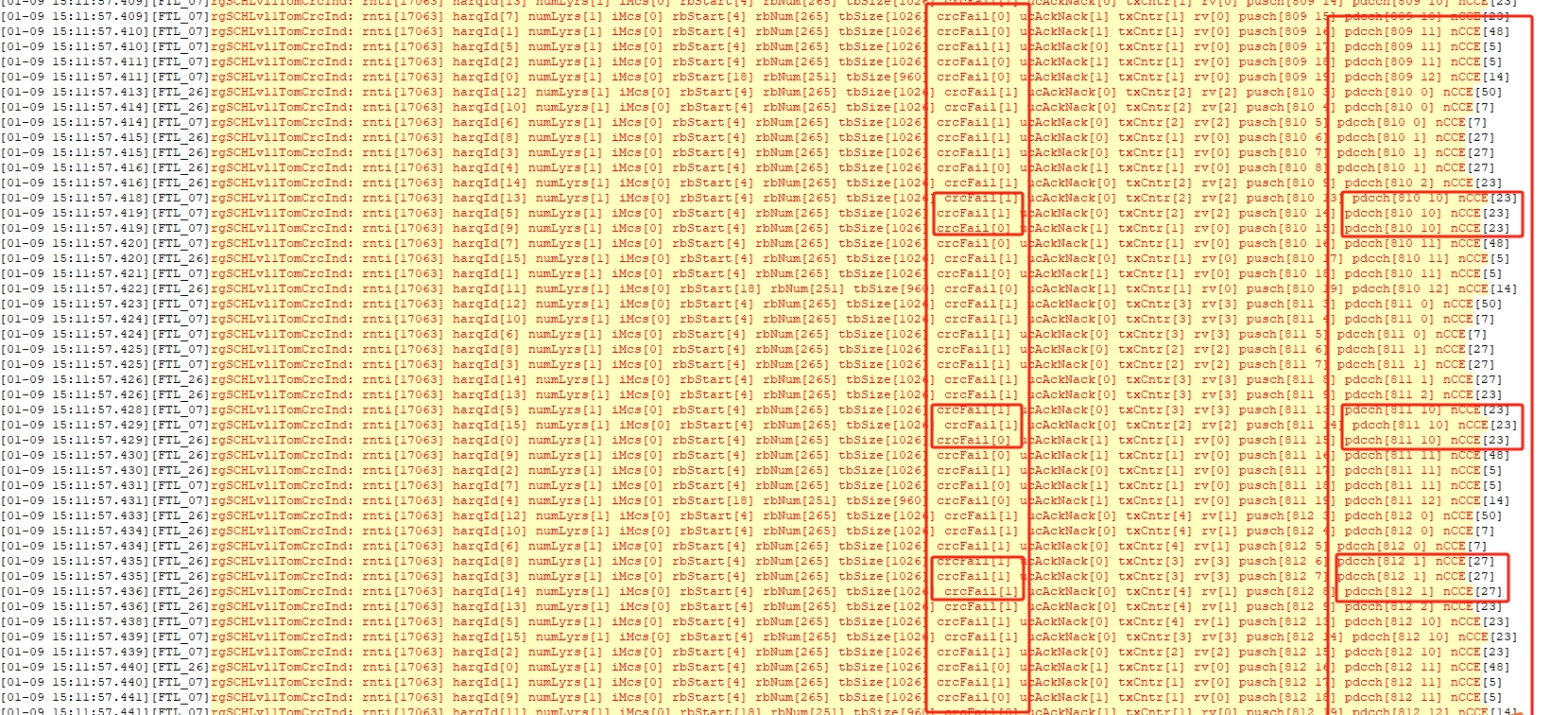

网上查找资料后发现,在多UE场景,这种PDCCH发生冲突属于正常现象,统计128UE的PDCCH分配失败比例,大约为0.1%,认为属于正常现象,对速率以及调度无影响