错误 #308

数字域环回样点偏移

状态:

已关闭

优先级:

一般

指派给:

-

类别:

FPGA

开始日期:

2020-12-29

计划完成日期:

2021-01-14

% 完成:

100%

预期时间:

问题归属:

描述

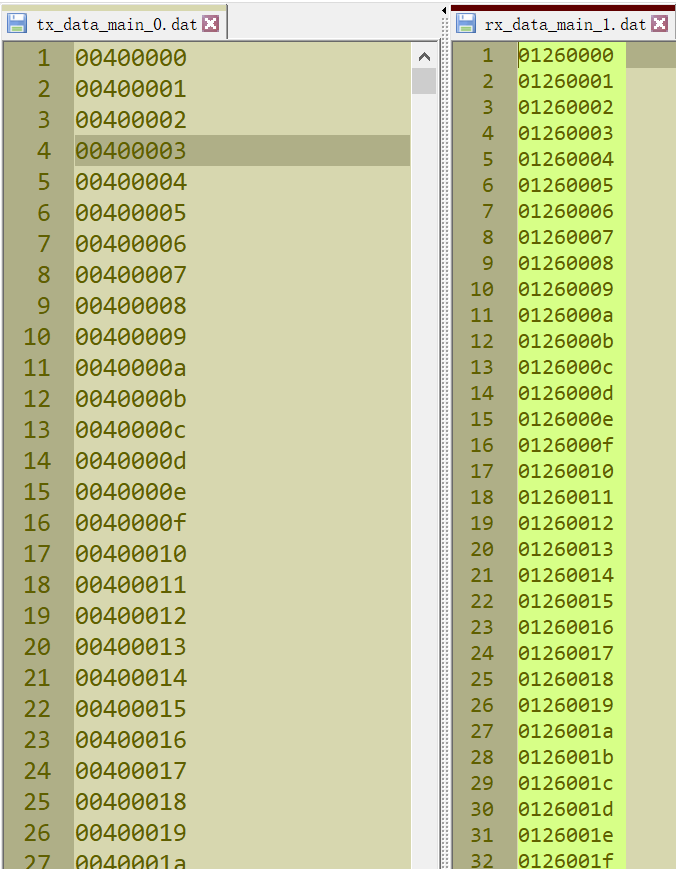

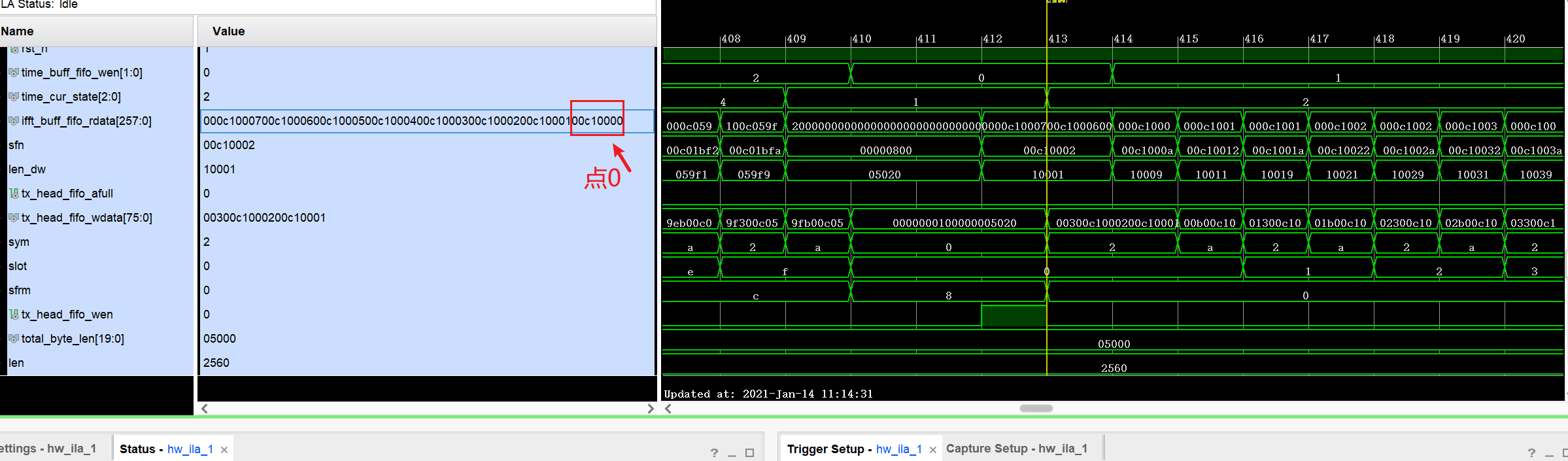

现象:数字域环回 样点滞后一个

现象:不进行make及softbin'编译,sys.log无法进行查看

文件

历史记录

由 匿名用户 更新于 超过 5 年 之前

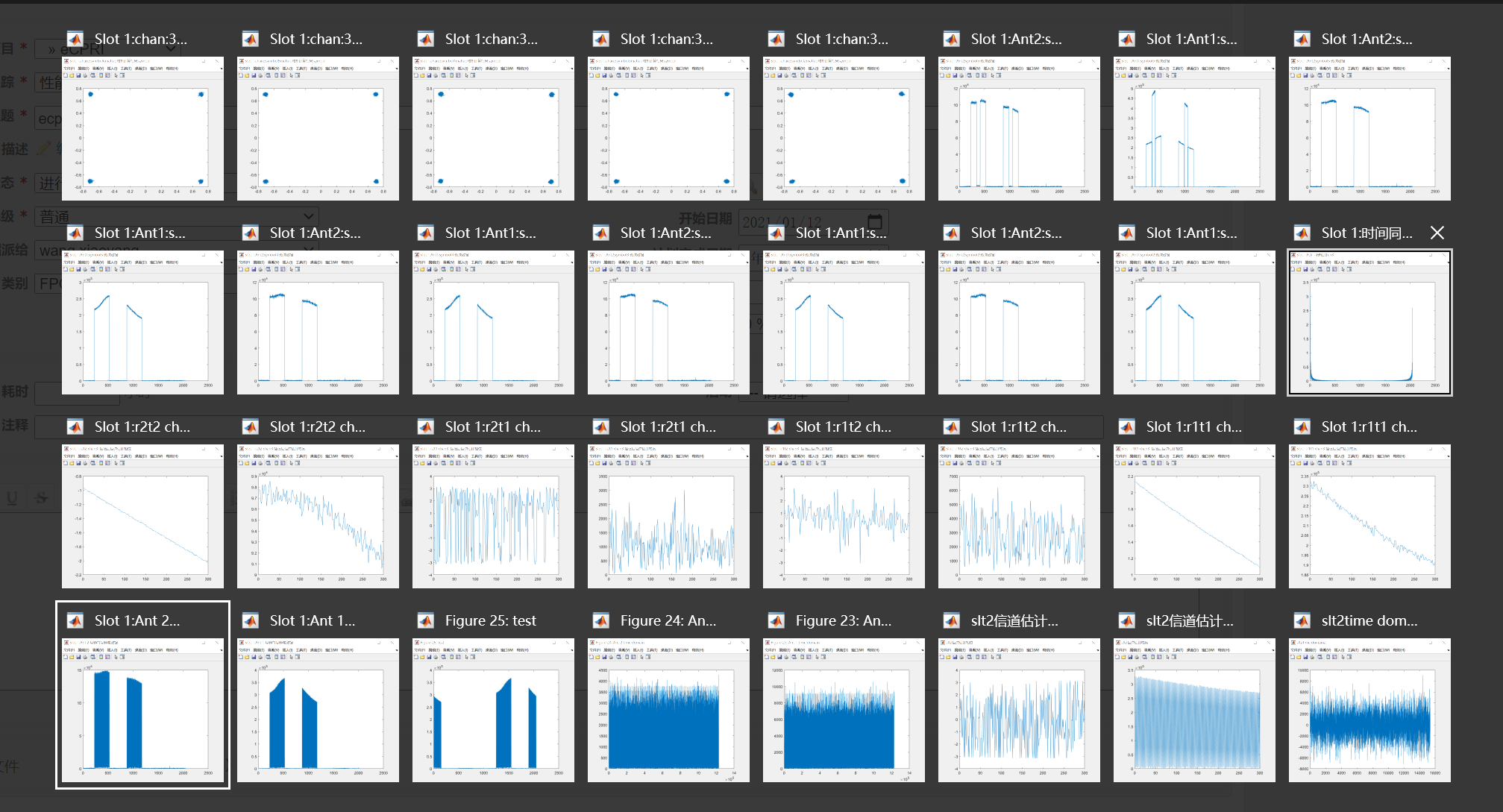

- 文件 ru射频模块采数.png ru射频模块采数.png 已添加

- 文件 ru射频模块采数2.png ru射频模块采数2.png 已添加

- 文件 tx_antx_gather.png tx_antx_gather.png 已添加

由 匿名用户 更新于 超过 5 年 之前

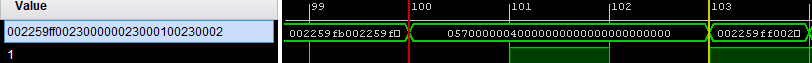

- 文件 样点修复.png 样点修复.png 已添加

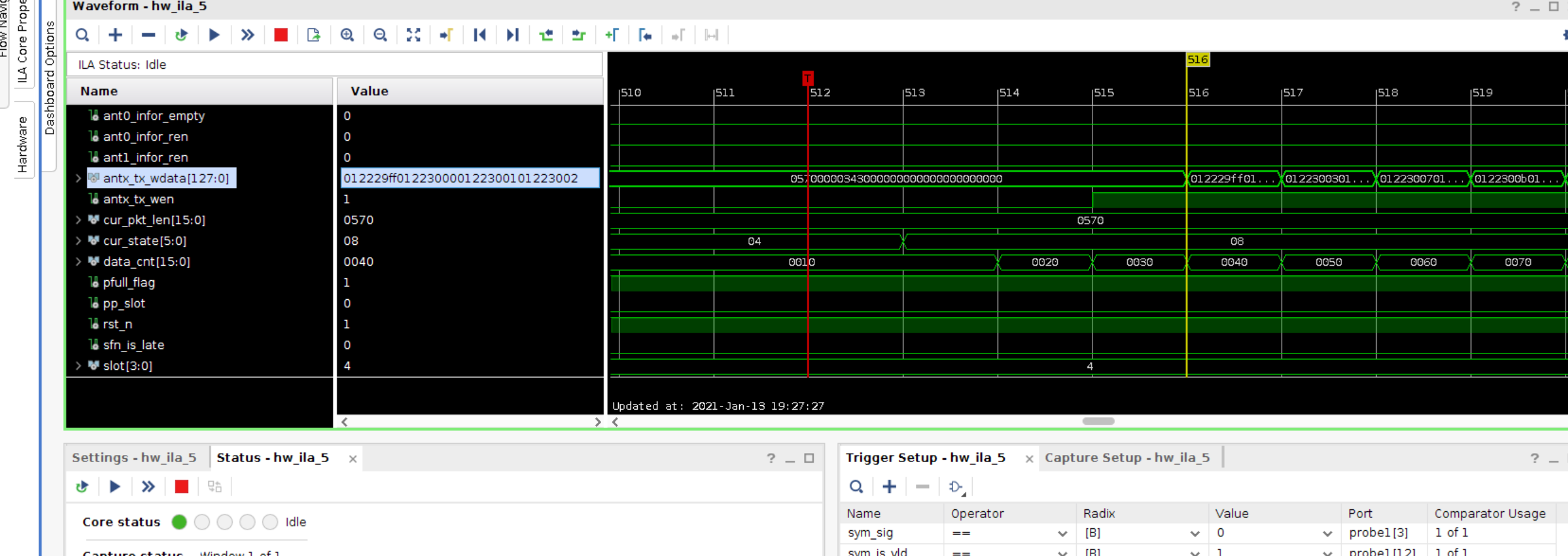

- 文件 xfft_dis入口.png xfft_dis入口.png 已添加

- % 完成 从 20 变更为 100

经过定位,是xfft的fifo未使用first word fall through模式,导致fh tx,将复位数据0当做第一个数据写入

如下图

上级fifo位置:xfft_top_u/tx_ifft_top_u/ifft_ip_ctrl_u/bk_fifo_8192x32b

* 修复后的样点*