错误 #3881

CPRI板卡,发送端信号与trigger信号之间存在6us左右时偏

由 高 峰 在 7 个月 之前添加.

更新于 5 个月 之前.

文件

历史记录

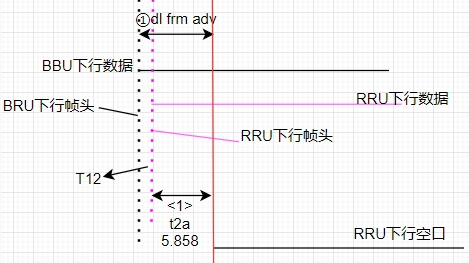

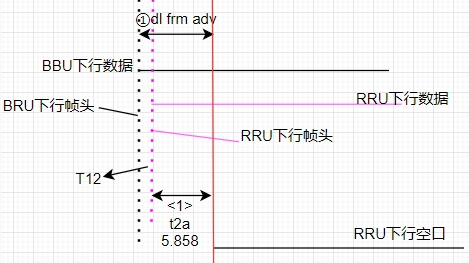

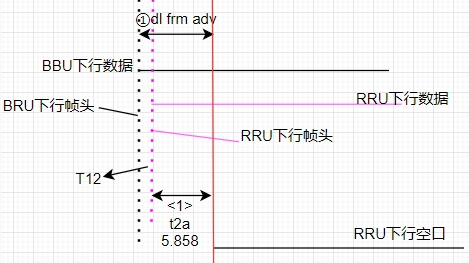

目前①配置为0

上研配置①: devmem 0x0A4F223C 32 0x161C(5.66us),需要在PHY加载后,协议栈启动之前配置。

使用cpri板卡---板卡测试,pdelay缩小到112了(此时tci/data还是没解开)。

重新配置下面三个寄存器,使用cp自校准版本,两块横联板卡可以解对pdsch。

devmem 0x0A4F223C 32 0xE80 #该寄存器对应DL Frame Advance

devmem 0x0A4F2238 32 0x999 #该寄存器对应UL Frame Delay

devmem 0x0A4F2234 32 0x1FFD #该寄存器对应Tul

导出 Atom

PDF