功能 #405

由 匿名用户 在 超过 5 年 之前添加.

更新于 大约 5 年 之前.

描述

需求:从sync_prach代码(fr2.0对应的fpga固件)中,移植tdd模块到pru中,并测试通过

文件

历史记录

- 计划完成日期 从 2021-01-21 变更为 2021-01-29

由 匿名用户 更新于 超过 5 年 之前

①确认zynq的中断及轮询机制

②确认arm读取fpga的寄存器机制

③TDD功能的实现

由 匿名用户 更新于 超过 5 年 之前

进度:

①TDD的设计关闭,包括FPGA部分的状态机、模块、引脚。

②暂时无法建立轻量系统

计划:

①直接在ecpri_wi的ru工程建立PL部分中断逻辑,使用vio控制;

②以及PS部分中断逻辑,使用PS部分的串口进行调试。

③测试ps部分无问题,开发PL部分TDD/GPIO逻辑

④测试PL/PS联调

由 匿名用户 更新于 超过 5 年 之前

- 状态 从 新建 变更为 进行中

- % 完成 从 0 变更为 20

- 预期时间 从 8.00 小时 变更为 0.00 小时

由 匿名用户 更新于 超过 5 年 之前

完成Pps部分的纯中断逻辑测试,待合并入ps工程。

计划:

①直接在ecpri_wi的ru工程建立PL部分中断逻辑,使用vio控制;--》完成

②PS部分中断逻辑合并,使用Pl控制ps中断进行调试。--》进行中

③测试ps部分无问题,开发PL部分TDD/GPIO逻辑

④测试PL/PS联调

由 匿名用户 更新于 超过 5 年 之前

ps部分验证完毕,可以通过pl的控制,完成射频功率增大减小。目前使用irq中断。

进行pl部分逻辑开发

计划:

①直接在ecpri_wi的ru工程建立PL部分中断逻辑,使用vio控制;--》完成

②PS部分中断逻辑合并,使用Pl控制ps中断进行调试。--》完成

③测试ps部分无问题,开发PL部分TDD/GPIO逻辑--》

④测试PL/PS联调

由 匿名用户 更新于 超过 5 年 之前

tdd的pl代码编写完毕。准备进行仿真,简单测例,无问题后出版本联调。

计划:

①直接在ecpri_wi的ru工程建立PL部分中断逻辑,使用vio控制;--》完成

②PS部分中断逻辑合并,使用Pl控制ps中断进行调试。--》完成

③测试ps部分无问题,开发PL部分TDD/GPIO逻辑--》完成

④测试PL/PS联调--》进行中

由 匿名用户 更新于 超过 5 年 之前

仿真完毕。准备在板测试。

计划:

①直接在ecpri_wi的ru工程建立PL部分中断逻辑,使用vio控制;--》完成

②PS部分中断逻辑合并,使用Pl控制ps中断进行调试。--》完成

③测试ps部分无问题,开发PL部分TDD/GPIO逻辑--》完成

④测试PL/PS联调--》进行中

由 匿名用户 更新于 超过 5 年 之前

RU的tti及slot是ecpri恢复,目前使用该tti产生rx tti及sfn,供TDD模块使用

由 匿名用户 更新于 大约 5 年 之前

由于时钟问题,补充了时钟模块,以产生TDD所需的TX时钟脉冲及idx,RX脉冲,设计完毕,编写代码。

由 匿名用户 更新于 大约 5 年 之前

wi暂未开发,fr部分代码版本已出,正在解决工具软件问题

由 匿名用户 更新于 大约 5 年 之前

遇到各种问题进度卡住

①SDK软件一定几率闪退-》重启解决

②SDK软件出现eclips error等软件本身错误-》出现一次,重启解决

③需要跟老王协调硬件资源-》搭建新环境,缺少功率足够的适配器及对应接口的DC 12v线,后来使用直流电源进行供电,但是实验室人员走动频繁空闲狭小,不够安全。应当物料采购,使用适配器供电。

④新的ru代码不稳定,回退旧版本-》多次回退及重新生成固件,仅一次crc正确。最后怀疑是fpga的du固件未下载。

⑤代码合并完毕,但假的调测无法观察

a.ila时钟问题,,必须由du给ru提供时钟,无电路原理图,无法找到免驱时钟。

b.非ila的调测信号过多,导致工程单次编译时间40分钟。去除调测后,有部分手动标记阻碍ila核心的识别,反复去除,最后编译时间13分钟。。

⑥ecpri fr的平台几乎100%段错误,需要先对du上电,后对ru上电,再对du重启-》多次重启及45秒等待浪费了相当的时间。

⑦使用直流电源搭建新的测试环境,由于遇到问题过多,忘记更新DU固件-》平台检测固件有问题,继续运行而不终止。

⑧USB线接触不良导致SDK报错,无法烧写固件-》疑似接触不良,最初怀疑固件生成问题,反复生成固件,浪费相当的时间。

⑨生成固件的步骤复杂,不确定是否步骤出现问题,由于远程卡顿加软件本身卡顿、数据传输不方便,对调试进度有阻碍。

⑩固化du的固件,使用稳定版ru固件,仍然段错误,新的ru硬件疑似问题。

由 匿名用户 更新于 大约 5 年 之前

进度:

①已经测试tdd模块使能关闭情况下,crc正确

②无法烧写ru问题,疑似软件bug,重启系统可以烧写。

③使用新购买的下载线,验证得旧下载线存在接触问题

④仿真+在板发现部分tdd bug,已定位,待 在板测试

由 匿名用户 更新于 大约 5 年 之前

计划:

①直接在ecpri_wi的ru工程建立PL部分中断逻辑,使用vio控制;--》完成

②PS部分中断逻辑合并,使用Pl控制ps中断进行调试。--》完成

③测试ps部分无问题,开发PL部分TDD/GPIO逻辑--》完成

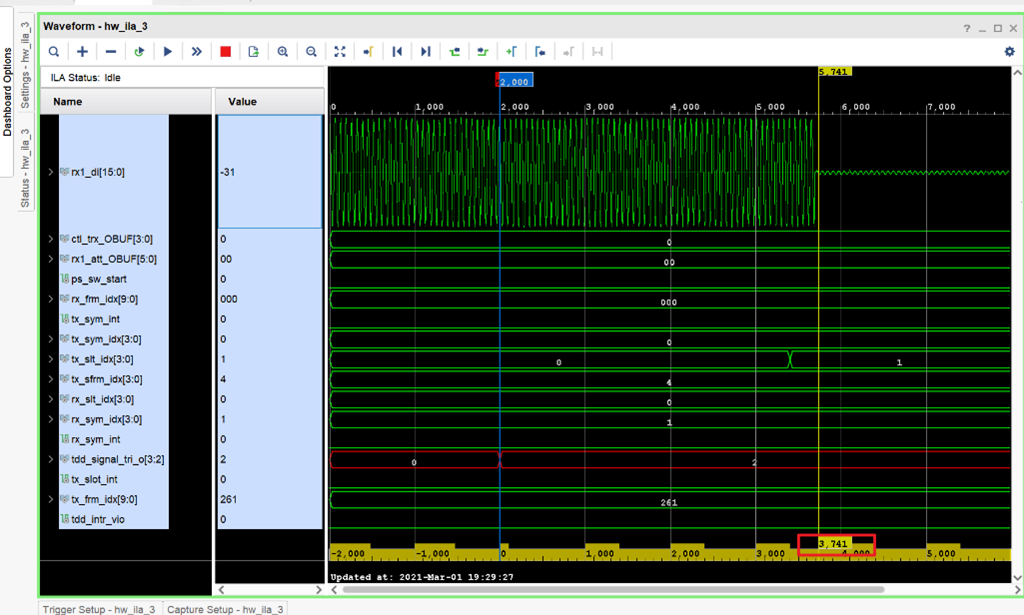

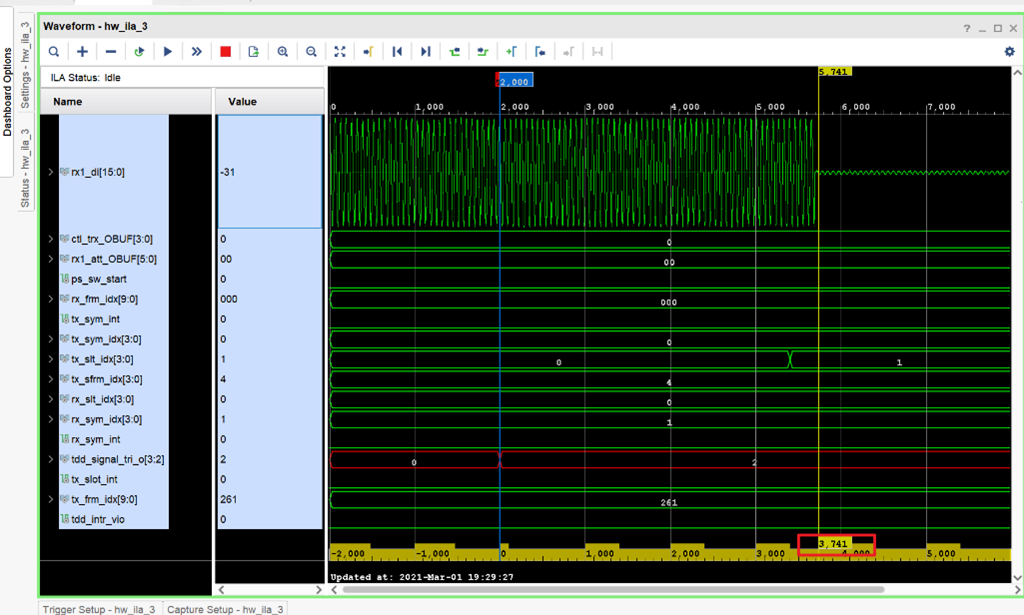

④测试PL/PS联调--》测试控制信号符合切换时序要求,需进一步确认收发信号。

由 匿名用户 更新于 大约 5 年 之前

计划:

①直接在ecpri_wi的ru工程建立PL部分中断逻辑,使用vio控制;--》完成

②PS部分中断逻辑合并,使用Pl控制ps中断进行调试。--》完成

③测试ps部分无问题,开发PL部分TDD/GPIO逻辑--》完成

④测试PL/PS联调--》测试控制信号符合切换时序要求,需进一步确认收发信号。

发射信号可以进行切换,输出功率约20dbm,需要对其他3路通道增加负载;

接收无法收到信号,rx_di/dq=0,疑似tdd pl逻辑切换导致jesd204 rx的ip挂死

待分别确认引脚分配、axi总线情况、trx_ctl及rx_att情况

由 匿名用户 更新于 大约 5 年 之前

现象:

①tdd导致的204brx挂死问题无复现,另起一个问题挂起。

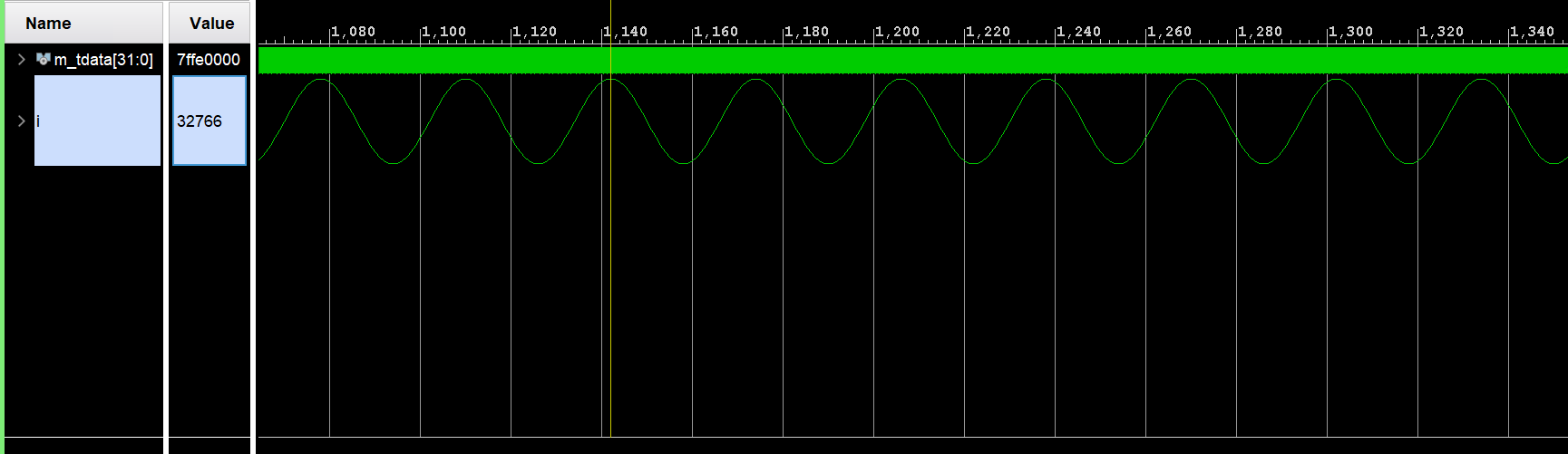

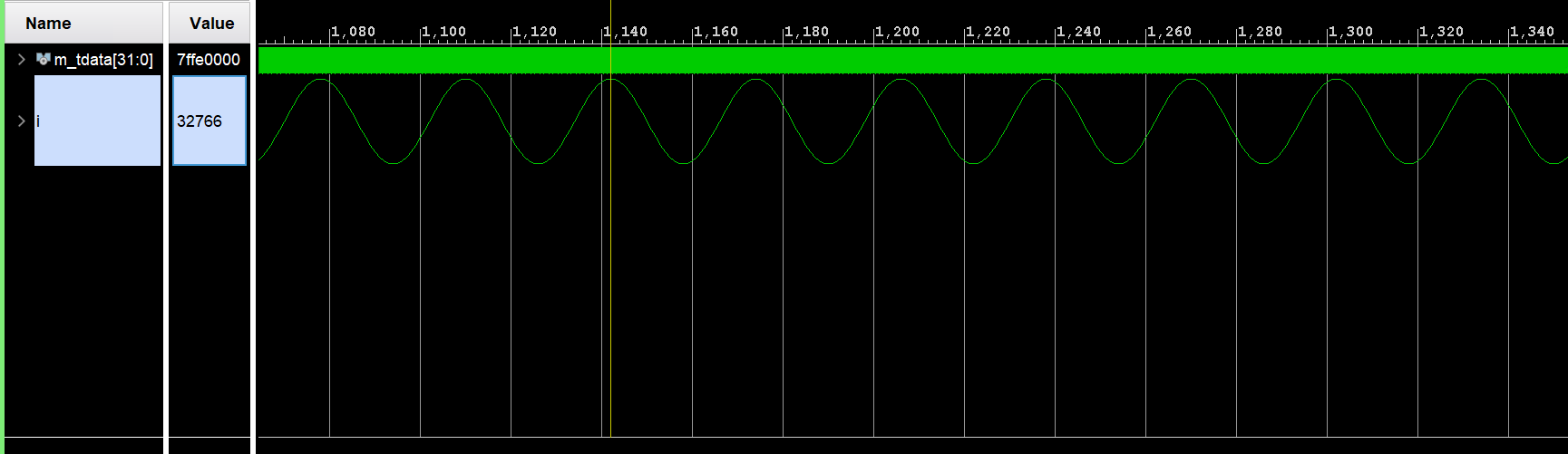

②目前测试,使用另外电脑发出单音,tdd rx可以在正确的时间点看到波形切换。

③tx无法直观测出,但频谱仪观察tx波形有切换,对应控制信号时序正确。

结论:tdd fr部分目前可用

计划:

①对tdd fr进行验证测试

②编写并测试tdd wi

由 匿名用户 更新于 大约 5 年 之前

①T/R切换CTL_TRX1时延

②ps中断生效时延

③接收功率定标、切换下发送功率差别

由 匿名用户 更新于 大约 5 年 之前

测试如下:

①rx接收底噪很低,幅值67左右

②rx的接收饱和点约-16.7dbm

③9371的tx衰减、rx增益,幅度符合理论值

④GPIO的rx 衰减,不符合理论值,如16dbm,实际只有5dbm

⑤T/R开关的隔离度是-48-21=-69dbm

⑥T/R开关的切换时间均在1.7us左右

⑦ps的9371衰减增益时间超出3000点,不符合预期,需要进行精确测量。

附文档《ru_tdd移植1.1.docx》,见5.4补充测试

由 匿名用户 更新于 大约 5 年 之前

①ps-9371 部分生效时间

②接收饱和点-16.7dbm 偏大

③rx att(gpio) 实际值小于理论值

④9371衰减只有26db,理论值41.95db

⑤tx dds的功率是否打满

由 匿名用户 更新于 大约 5 年 之前

经过确认,tx的输出功率最大值24dbm 使用dds测得

U-》D下,切换,ps部分从中断功能完毕到功率变化生效,花费时间3700点远超预期值。

由 匿名用户 更新于 大约 5 年 之前

周一周二对《FPGA RU_TDD测试.xlsx》的内容进行测试

①解决rx gpio att数值不匹配问题

之前测试漏写bit5,故理论值31.5dbm,实测只有一半。

②最大发射功率约27dBm

③3.4-3.8的功率在2.6~2.7dBm

④接收最大值-34dBm,最大增益底噪-83dBm,接收最小值-63dBm,最小增益底噪-61.6dBm

⑤rx gpio att的调整值跟理论值吻合,调整时间151点约1.23us

⑥ctl trx的切换,1->0 220点, 0->1 202点

⑦ctl trx切换,隔离度65dBm,但trx = 1时,隔离度只有40

⑧信号接收时序符合要求

待完成

①接收底噪抬升测试

②发送时序测试

由 匿名用户 更新于 大约 5 年 之前

①发送时序根据TC004002,TX的TDD周期为5ms符合设计,但是20ms的周期内,TDD的最后上升沿是19.800ms处,200us的时间差无法解释,认为是频谱仪采数延迟或通道生效延时,暂时挂起

②发送底噪抬升根据TC003005,影响较小,9371tx_att最小比最大时,底噪差距6dBm

③补充测试TC003004,收发开关切换的隔离度,认为隔离度在65dbm以上,但是出现tx的发送功率变化趋势跟rx功率异常情况。

④补充9371 tx att 测试tc004004,在41.95~13db时,符合理论值。10以下已经饱和,饱和发送功率为25dbm。可以解释TC003004中的rx接收功率异常问题。

由 匿名用户 更新于 大约 5 年 之前

- 状态 从 进行中 变更为 已解决

- % 完成 从 90 变更为 100

pRU工程文件合并

名称:R2F_FFB02_V_1_0_0_T210315

路径:http://192.168.1.104/YZRT/yzh/fpga_urllc/tree/Test

导出 Atom

PDF