错误 #4055

历史记录

由 赵 强 更新于 7 个月 之前

- 文件 img_v3_02q6_19215336-8832-4500-95ac-6eaebc61459g.jpg img_v3_02q6_19215336-8832-4500-95ac-6eaebc61459g.jpg 已添加

- 文件 屏幕截图 2025-09-16 165739.png 屏幕截图 2025-09-16 165739.png 已添加

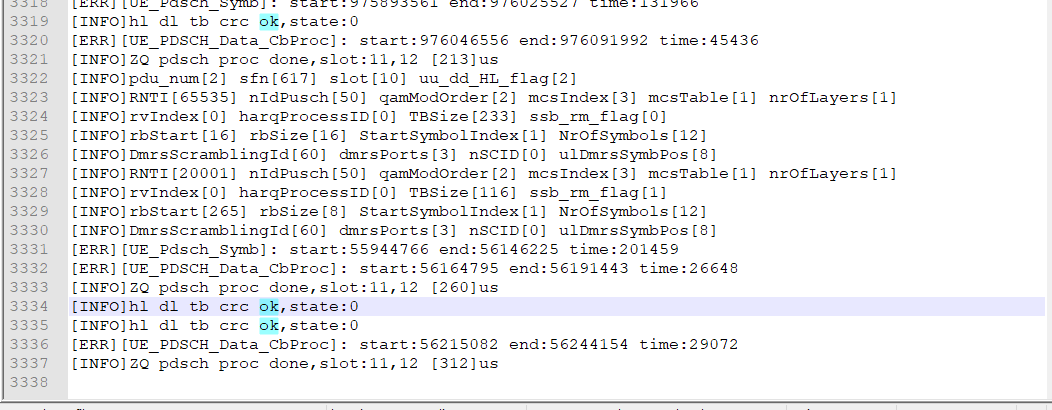

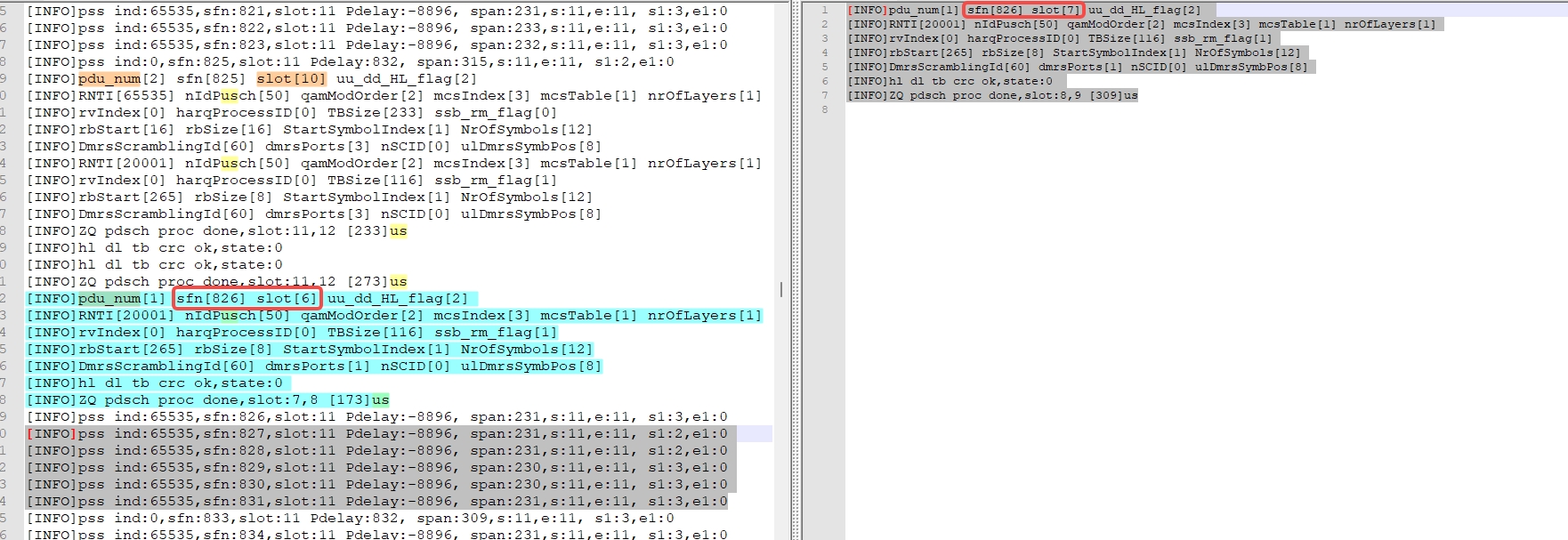

1.在core5上同时部署PDSCH与UE_Dl_Sync_Task任务,core6部署PDSCH任务。能够编译出版本,但是在分别触发PDSCH任务时,

在核5上,trigger完(826,6)PDSCH后,然后在核6上trigger(826,7)。这没有问题,都解对了。

但是要在核5上trigger (826,8),这个时候,PDCCH出现异常,没有再trigger了。怀疑此时PDSCH与UE_Dl_Sync_Task任务冲突导致。

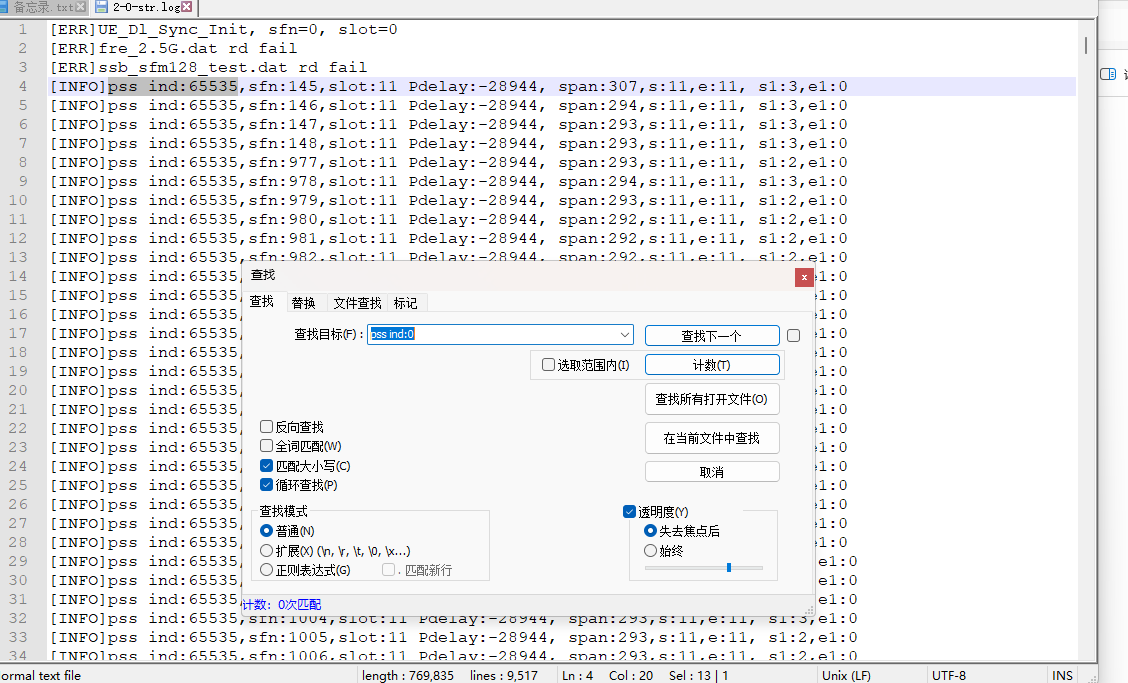

2.在1的基础上,将UE_Dl_Sync_Task任务移至核2后,PSS解不到。波姐协助排查。

由 赵 强 更新于 7 个月 之前

20250920工作日报:

1.拉取Hl_dev_2最新代码,只trigger core6 PDSCH任务,发现MCS最多只到3,再往高增加MCS,全部解错。

原因在与上周升级了RRU,恢复原来的版本后,MCS能够到27。

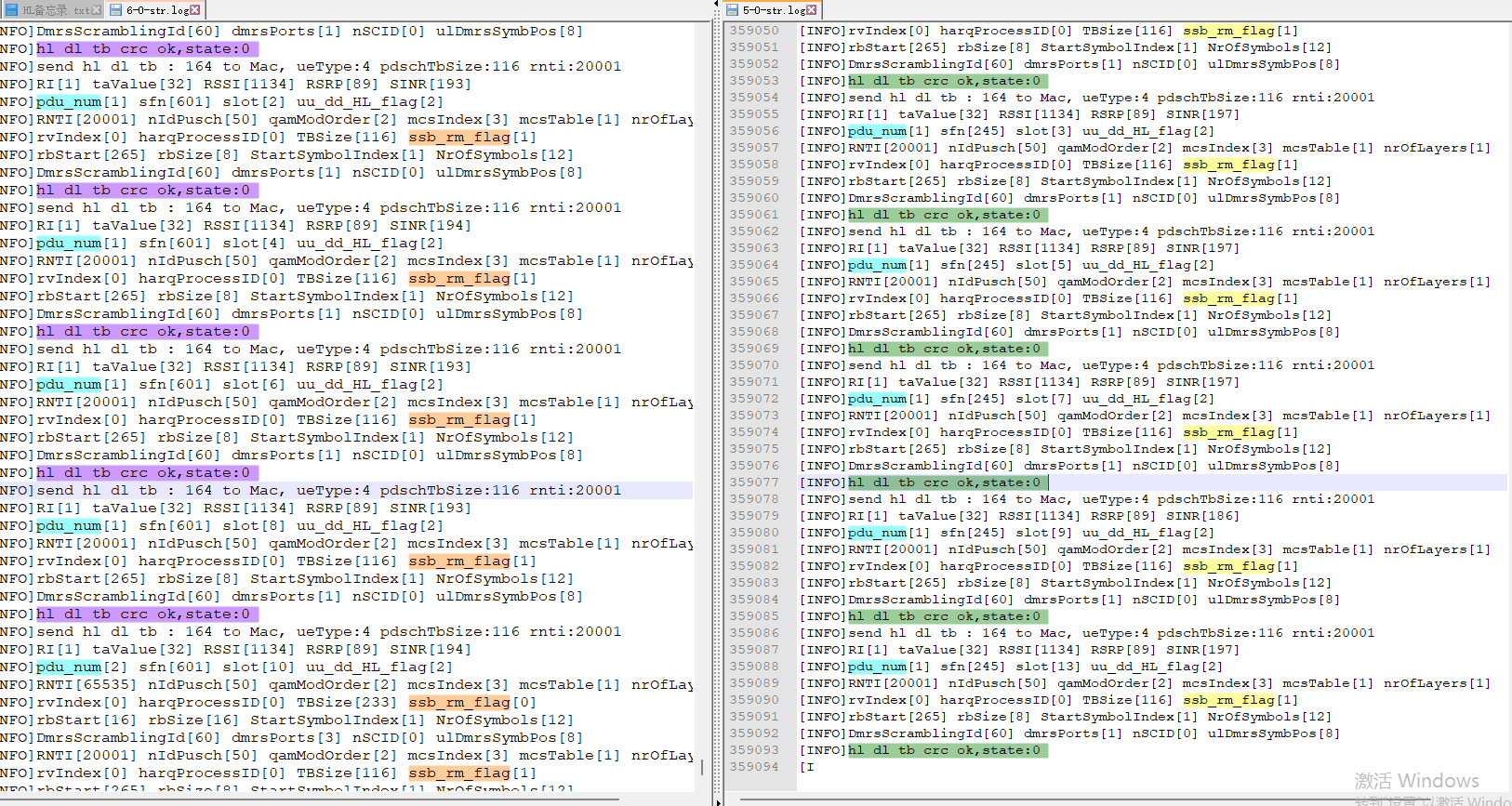

2.更改deofdm与PDSCH的接口代码,将deofdm的参数先从DM搬到DDR,PDSCH再从DDR把参数l搬到DM后,sfn/slot参数正常。

3.在2的基础上,只triiger core6 的PDSCH任务,静/动态时隙数据(TCI,TB)均能解对。只triiger core5 的PDSCH任务,静态时隙数据(TCI,TB)均能解对,但是动态时隙下,TCI没有解对,问题排查中。

由 赵 强 更新于 6 个月 之前

- 文件 img_v3_02qt_b2e9f8d8-e8c1-451e-a565-5ddd4e07a98g.jpg img_v3_02qt_b2e9f8d8-e8c1-451e-a565-5ddd4e07a98g.jpg 已添加

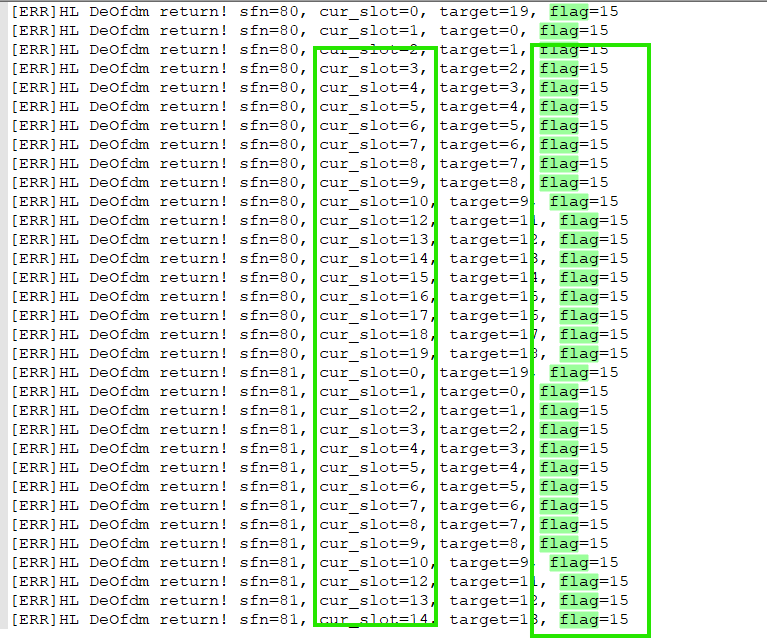

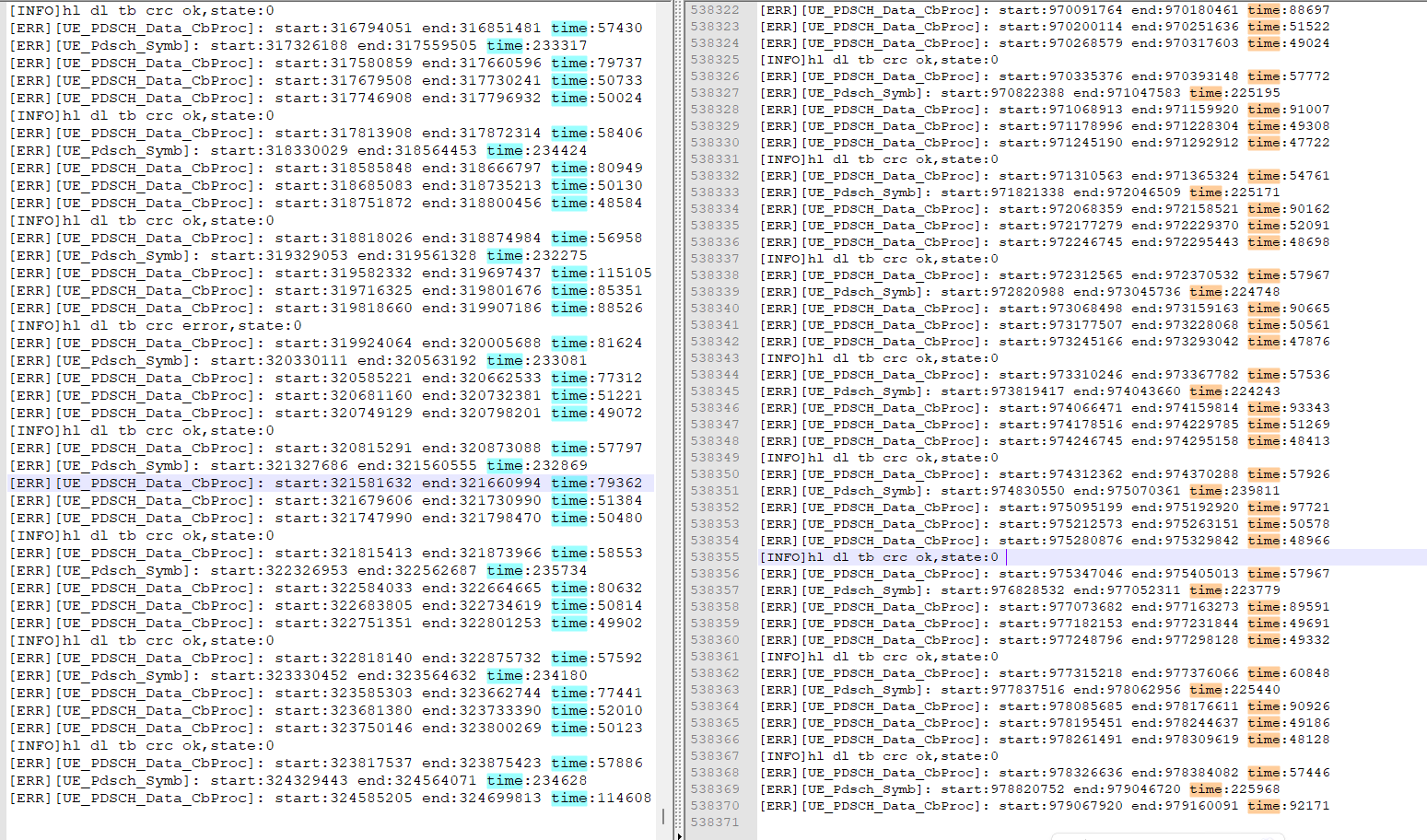

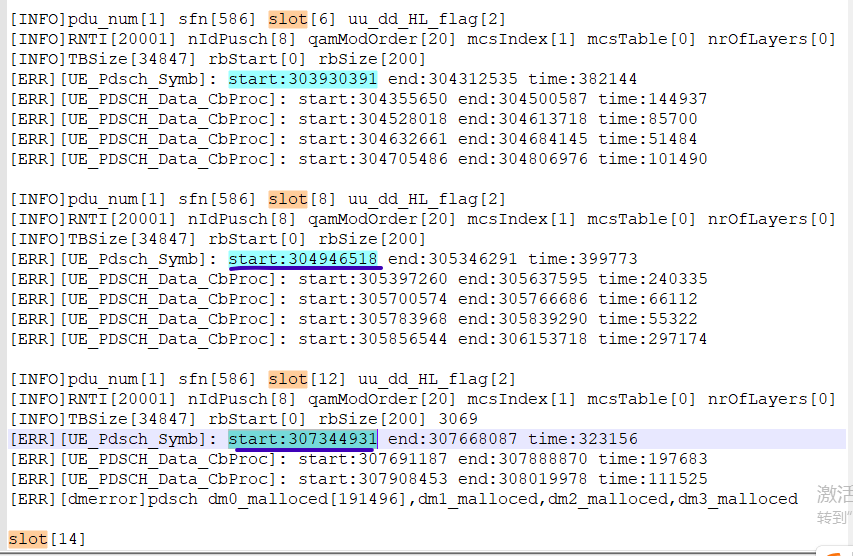

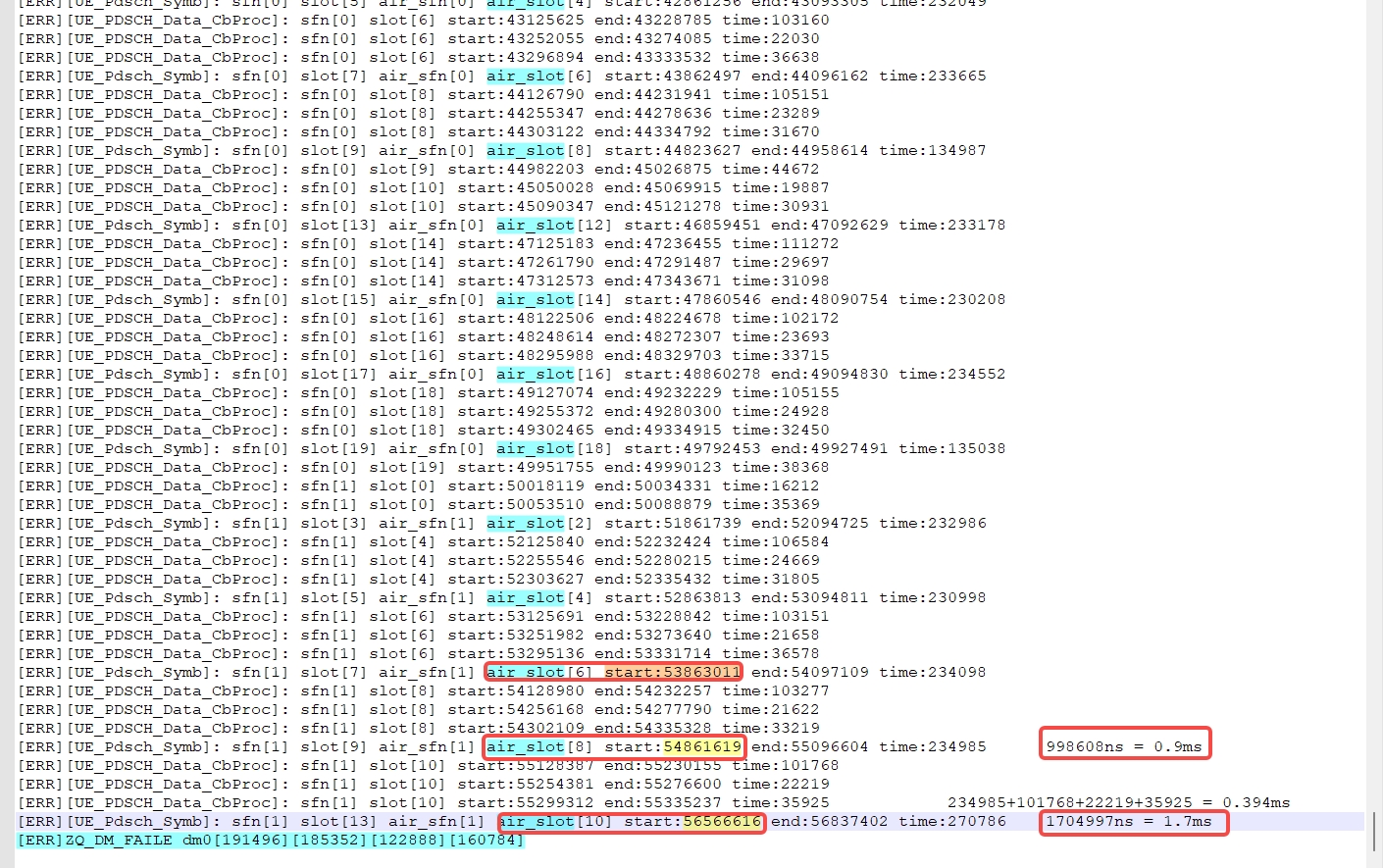

(1)slot6跟slot8之间trigger的间隔大概是1ms左右,这个是符合2个slot的预期的。

(2)但是sslot8跟lot10之间trigger的间隔就是1.7ms了,就不正常了。

(3)这块的超时导致slot10的任务只完成了sym的处理,bit级正在处理时,(有sym级的打印,没有bit级的打印),然后slot12的任务就被trigger了,导致slot12的DM空间申请不下来,从而挂死