错误 #4689

UU口测试,终端发msg4 ack在基站概率性解错

0%

描述

1,终端发msg4 ack在基站数据延迟约100-280点(小于cp,基站可以收到,对后续流程没有影响)。(发生概率1/20)

2,或迟约300点(大于cp,基站不能收到)。(发生概率比较低)

文件

相关的问题

历史记录

由 白 瑞朋 更新于 3 个月 之前

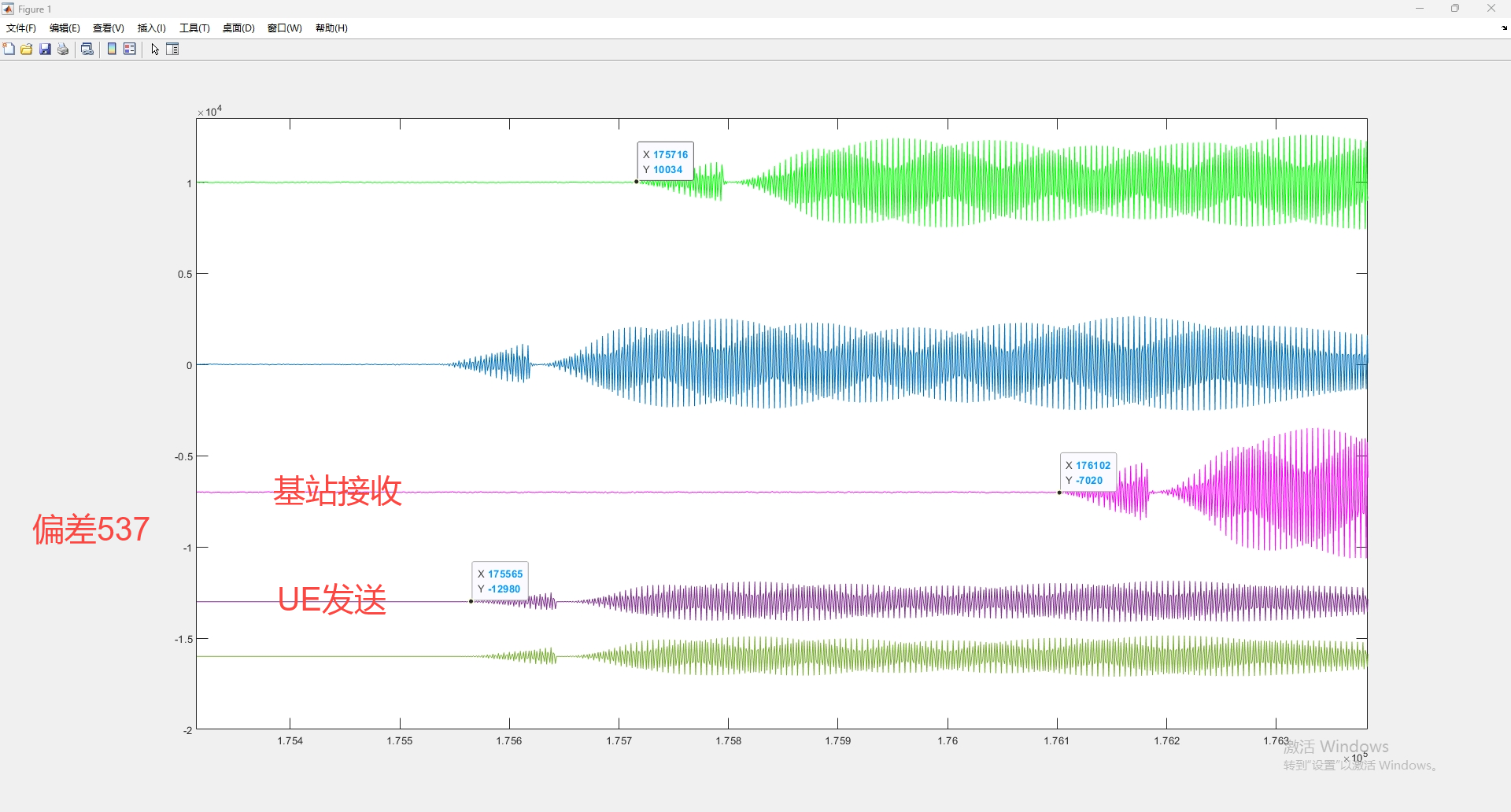

- 文件 基站接收滞后537个样点.png 基站接收滞后537个样点.png 已添加

- 文件 Hex_ack18.dat Hex_ack18.dat 已添加

- 文件 Hex_UL_TIMEDATA18.dat Hex_UL_TIMEDATA18.dat 已添加

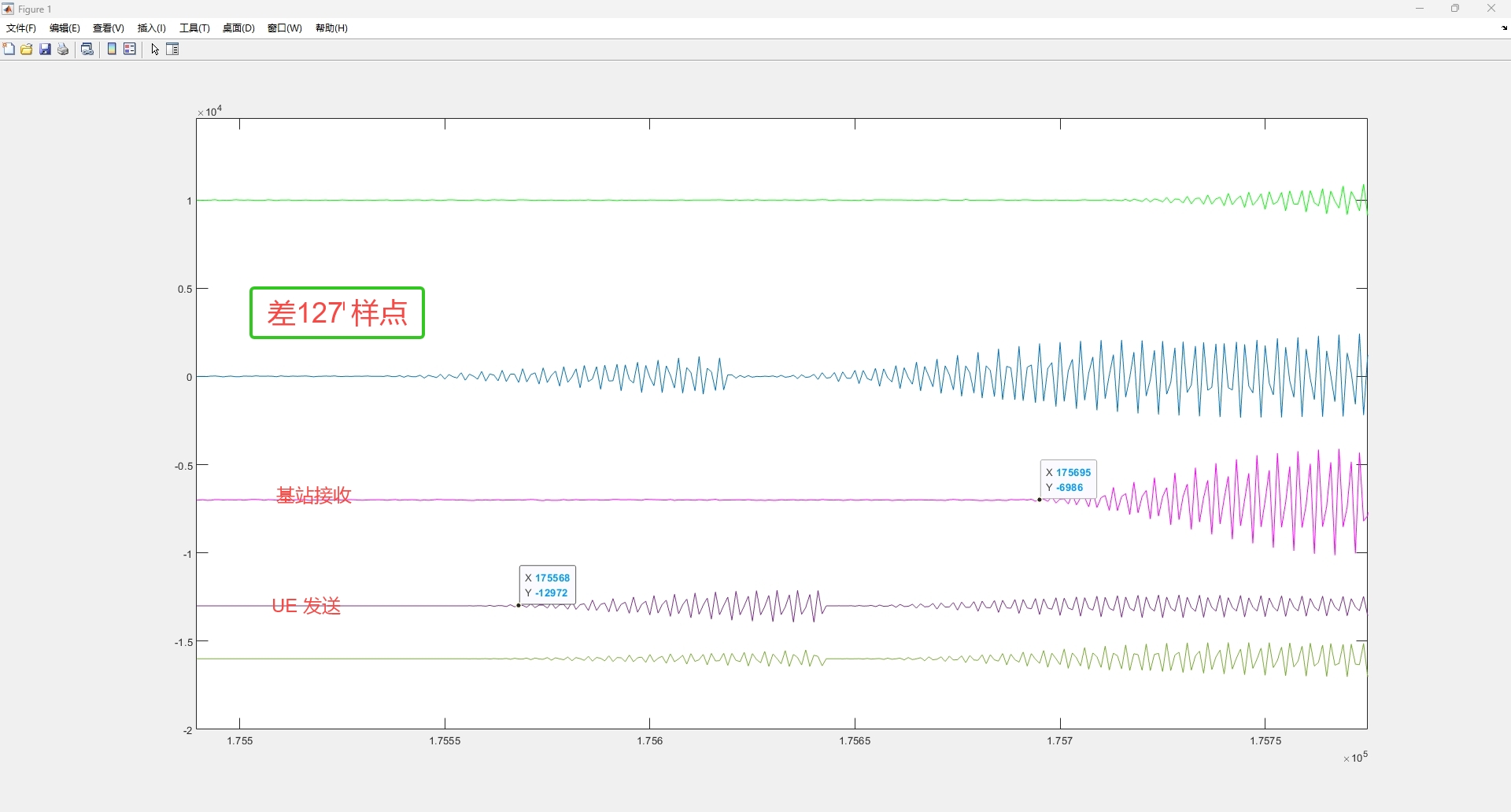

偏差537个样点

由 杨 晋 更新于 3 个月 之前

这个问题表现为两种现象:

1、终端可以接入,但概率性基站采数msg4 ack滞后一些样点(小于cp长度)。此时基站采数看到,后续sr和msg5等的位置是正常的,这种对后续流程应该没有影响。

2、当msg4 ack失败,基站采数msg4 ack滞后超过cp的样点,目前还未发现根因,不过概率较低。 ------如果终端有msg4 ack失败,重新发起接入的流程,推测是可以接入。

最近的一些测试:

1、回退CP 11.26和11.17版本,phy11.18版本,共测试43次出现一次msg4 ack失败,没有复现之前高概率msg4 ack失败(40%)情况。

2、phy屏蔽给CP的TA调整接口(CP不调TA),也有上面两种现象出现。

3、phy出了仅调试版本(msg4 ack后停止后续流程)+cp加调测版本,测试57次(其中基站数据可用39次,其他用FPGA采数确认),没有复现基站数据偏移,怀疑这两个版本配套就没问题了。

4、prachCfgIndex:从160改到155,测试30次,没有复现msg4 ack错误问题。(可接入时,CfgIndex=160,基站采集msg4 ack比终端位置提前20多~30多样点,CfgIndex=155, 基站采集msg4 ack比终端位置滞后20多~40多样点)

5、通过功分器和触发连线,使用FPGA采数,发生现象1基站采msg4 ack偏移时,FPGA采到的数据是完整的(基站采数只采调度时隙,所以看到数据不完整)。

6、phy加了个打桩功能不调度写任务和不清bufer,用devmem在80样点位置写毛刺数据,基站采数发现毛刺位置不稳定,某次在37~144之间,怀疑两块板卡有频偏引起。(某次出现msg4 ack失败,基站采数据滞后537样点,此时终端80位置打桩毛刺,基站采数3次,看到毛刺位置133、97、87)。

7、终端,phy有一次采出的msg4 ack数据,发现比正常位置滞后了一百多样点(测试这么久只出现过一次)。

已排除的一些可能原因(可能还需要再次确认):

1、平台和phy之间接口地址错误或被改写。

2、phy写的发射buffer内容被改写。(phy在cp开始写魔术字,平台中断0读取;以及phy在发msg4 ack的下个时隙再次采集发射buffer数据)

3、平台TA调整错误或多调了一次。

4、平台msg3和msg4之间,csu的开关发生变化。

5、msg1之后,jesd timer又被重启。

6、jesd 链表内容被改写。

7、基站原因。