错误 #580

物理层出现FH 过来的slot号跳变导致物理层挂死

开始日期:

2021-06-28

计划完成日期:

% 完成:

0%

预期时间:

问题归属:

系统

CPU类型:

描述

[06-28 10:23:59.988][DEBUG][FH-RX]phy_fpga_ul_iq_setup, SlotAdvIdx[4442] OneSymDataSize[13104] FirstHalfSlot[1] SymbMask[0x 7f] g_Stub_pusch_Data_switch[0]

[06-28 10:23:59.988][DEBUG][FH-RX]phy_fpga_ul_iq_setup, SlotAdvIdx[4442] OneSymDataSize[13104] FirstHalfSlot[0] SymbMask[0x3f80] g_Stub_pusch_Data_switch[0]

[06-28 10:23:59.988][DEBUG][FH-RX]phy_fpga_ul_iq_setup, SlotAdvIdx[4443] OneSymDataSize[13104] FirstHalfSlot[1] SymbMask[0x 7f] g_Stub_pusch_Data_switch[0]

[06-28 10:23:59.988][DEBUG][FH-RX]phy_fpga_ul_iq_setup, SlotAdvIdx[4443] OneSymDataSize[13104] FirstHalfSlot[0] SymbMask[0x3f80] g_Stub_pusch_Data_switch[0]

[06-28 10:23:59.989][DEBUG][FH-RX]phy_fpga_ul_iq_setup, SlotAdvIdx[4444] OneSymDataSize[13104] FirstHalfSlot[1] SymbMask[0x 7f] g_Stub_pusch_Data_switch[0]

[06-28 10:23:59.989][DEBUG][FH-RX]phy_fpga_ul_iq_setup, SlotAdvIdx[4444] OneSymDataSize[13104] FirstHalfSlot[0] SymbMask[0x3f80] g_Stub_pusch_Data_switch[0]

[06-28 10:23:59.989][DEBUG][FH-RX]phy_fpga_ul_iq_setup, SlotAdvIdx[4445] OneSymDataSize[13104] FirstHalfSlot[1] SymbMask[0x 7f] g_Stub_pusch_Data_switch[0]

[06-28 10:23:59.989][DEBUG][FH-RX]phy_fpga_ul_iq_setup, SlotAdvIdx[4445] OneSymDataSize[13104] FirstHalfSlot[0] SymbMask[0x3f80] g_Stub_pusch_Data_switch[0]

[06-28 10:23:59.990][DEBUG][FH-RX]phy_fpga_ul_iq_setup, SlotAdvIdx[4446] OneSymDataSize[13104] FirstHalfSlot[1] SymbMask[0x 7f] g_Stub_pusch_Data_switch[0]

[06-28 10:23:59.990][DEBUG][FH-RX]phy_fpga_ul_iq_setup, SlotAdvIdx[4446] OneSymDataSize[13104] FirstHalfSlot[0] SymbMask[0x3f80] g_Stub_pusch_Data_switch[0]

[06-28 10:23:59.990][DEBUG][FH-RX]phy_fpga_ul_iq_setup, SlotAdvIdx[4447] OneSymDataSize[13104] FirstHalfSlot[1] SymbMask[0x 7f] g_Stub_pusch_Data_switch[0]

[06-28 10:23:59.990][DEBUG][FH-RX]phy_fpga_ul_iq_setup, SlotAdvIdx[4447] OneSymDataSize[13104] FirstHalfSlot[0] SymbMask[0x3f80] g_Stub_pusch_Data_switch[0]

[06-28 10:23:59.991][DEBUG][FH-RX]phy_fpga_ul_iq_setup, SlotAdvIdx[4448] OneSymDataSize[13104] FirstHalfSlot[1] SymbMask[0x 7f] g_Stub_pusch_Data_switch[0]

[06-28 10:23:59.991][DEBUG][FH-RX]phy_fpga_ul_iq_setup, SlotAdvIdx[4448] OneSymDataSize[13104] FirstHalfSlot[0] SymbMask[0x3f80] g_Stub_pusch_Data_switch[0]

[06-28 10:23:59.991][DEBUG][FH-RX]phy_fpga_ul_iq_setup, SlotAdvIdx[4449] OneSymDataSize[13104] FirstHalfSlot[1] SymbMask[0x 7f] g_Stub_pusch_Data_switch[0]

[06-28 10:23:59.991][DEBUG][FH-RX]phy_fpga_ul_iq_setup, SlotAdvIdx[4449] OneSymDataSize[13104] FirstHalfSlot[0] SymbMask[0x3f80] g_Stub_pusch_Data_switch[0]

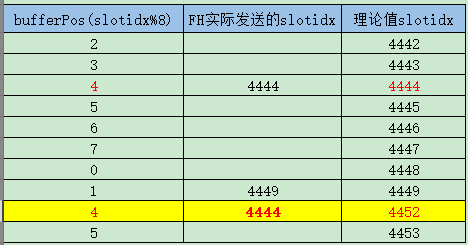

[06-28 10:23:59.993][DEBUG][FH-RX]phy_fpga_ul_iq_setup, SlotAdvIdx[4444] OneSymDataSize[13104] FirstHalfSlot[1] SymbMask[0x 7f] g_Stub_pusch_Data_switch[0] ///slot应该是4452 但是前传实际发送过来的为4444

[06-28 10:23:59.993][DEBUG][FH-RX]phy_fpga_ul_iq_setup, SlotAdvIdx[4444] OneSymDataSize[13104] FirstHalfSlot[0] SymbMask[0x3f80] g_Stub_pusch_Data_switch[0] // slot应该是4452 但是前传实际发送过来的为4444

[06-28 10:23:59.993][DEBUG][FH-RX]phy_fpga_ul_iq_setup, SlotAdvIdx[4453] OneSymDataSize[13104] FirstHalfSlot[1] SymbMask[0x 7f] g_Stub_pusch_Data_switch[0]

[06-28 10:23:59.993][DEBUG][FH-RX]phy_fpga_ul_iq_setup, SlotAdvIdx[4453] OneSymDataSize[13104] FirstHalfSlot[0] SymbMask[0x3f80] g_Stub_pusch_Data_switch[0]

[06-28 10:23:59.994][DEBUG][FH-RX]phy_fpga_ul_iq_setup, SlotAdvIdx[4454] OneSymDataSize[13104] FirstHalfSlot[1] SymbMask[0x 7f] g_Stub_pusch_Data_switch[0]

[06-28 10:23:59.994][DEBUG][FH-RX]phy_fpga_ul_iq_setup, SlotAdvIdx[4454] OneSymDataSize[13104] FirstHalfSlot[0] SymbMask[0x3f80] g_Stub_pusch_Data_switch[0]

文件

相关的问题

历史记录

由 匿名用户 更新于 将近 5 年 之前

在驱动侧增加定位问题的打印,打印如下,等待问题复现:

frame = (nFthCallBackStat>>11)&0x000003ff;

subframe = (nFthCallBackStat>>5)&0x0000003f;

slot = (nFthCallBackStat)&0x0000001f;

tmpSlotIdx = frame*20 + subframe*2 + slot;

tmpSlotIdx1 = gTxTimeInd.bit.nFrameIdx*10*2 + gTxTimeInd.bit.nSubFrameIdx*2 + gTxTimeInd.bit.nSlotIdx;

if (((tmpSlotIdx < 20479) && (tmpSlotIdx+1 != tmpSlotIdx1)) || ((20479 == tmpSlotIdx) && (tmpSlotIdx1 != 0)))

{

zLog(PHY_LOG_ERROR, "[DRV] FH_Rx, header[%d,%d,%d] SlotIdx[%d] TTI_time[%d,%d,%d] TTIslotIdx[%d]",

frame, subframe,slot, tmpSlotIdx, gTxTimeInd.bit.nFrameIdx, gTxTimeInd.bit.nSubFrameIdx, gTxTimeInd.bit.nSlotIdx, tmpSlotIdx1);

}

pFthRxElement->pCallback((void*)pFthRxElement->pDstBuf, nFthCallBackStat); /*cpa_fh_rx_callback()*/

由 匿名用户 更新于 超过 4 年 之前

- 文件 yzrt_l1_20210719183108.log yzrt_l1_20210719183108.log 已添加

- 目标版本 从 Rel_2.1.6 变更为 Rel_2.1.8

大上行配比情况下,FH rx过来的数据头中的slot打印和tti中的打印出现了不一致的情况如下:(偶现)

[07-19 18:32:12.299][ERROR][DRV] FH_Rx, header[1022,8,1] SlotIdx[20457] TTI_time[1023,0,0] TTIslotIdx[20460]

[07-19 18:32:12.300][ERROR][DRV] FH_Rx, header[1022,9,1] SlotIdx[20459] TTI_time[1023,1,0] TTIslotIdx[20462]

[07-19 18:32:12.301][ERROR][DRV] FH_Rx, header[1023,0,1] SlotIdx[20461] TTI_time[1023,2,0] TTIslotIdx[20464]

[07-19 18:32:12.302][ERROR][DRV] FH_Rx, header[1023,1,1] SlotIdx[20463] TTI_time[1023,3,0] TTIslotIdx[20466]

[07-19 18:32:12.303][ERROR][DRV] FH_Rx, header[1023,2,1] SlotIdx[20465] TTI_time[1023,4,0] TTIslotIdx[20468]

[07-19 18:32:12.304][ERROR][DRV] FH_Rx, header[1023,3,1] SlotIdx[20467] TTI_time[1023,5,0] TTIslotIdx[20470]

[07-19 18:32:12.305][ERROR][DRV] FH_Rx, header[1023,4,1] SlotIdx[20469] TTI_time[1023,6,0] TTIslotIdx[20472]

[07-19 18:32:12.306][ERROR][DRV] FH_Rx, header[1023,5,1] SlotIdx[20471] TTI_time[1023,7,0] TTIslotIdx[20474]

[07-19 18:32:12.307][ERROR][DRV] FH_Rx, header[1023,6,1] SlotIdx[20473] TTI_time[1023,8,0] TTIslotIdx[20476]

由 匿名用户 更新于 超过 4 年 之前

近期 出现了很多次该问题的挂死,现象都一致,而且发现 FH发送过来的数据头中的slot都是奇数的有问题,偶数的和tti的是对应的。

[07-27 15:35:33.379][ERROR][DRV] FH_Rx, header[1019,1,1] SlotIdx[20383] TTI_time[1019,3,0] TTIslotIdx[20386]

[07-27 15:35:33.380][ERROR][DRV] FH_Rx, header[1019,2,1] SlotIdx[20385] TTI_time[1019,4,0] TTIslotIdx[20388]

[07-27 15:35:33.381][ERROR][DRV] FH_Rx, header[1019,3,1] SlotIdx[20387] TTI_time[1019,5,0] TTIslotIdx[20390]

[07-27 15:35:33.382][ERROR][DRV] FH_Rx, header[1019,4,1] SlotIdx[20389] TTI_time[1019,6,0] TTIslotIdx[20392]

[07-27 15:35:33.383][ERROR][DRV] FH_Rx, header[1019,5,1] SlotIdx[20391] TTI_time[1019,7,0] TTIslotIdx[20394]

[07-27 15:35:33.384][ERROR][DRV] FH_Rx, header[1019,6,1] SlotIdx[20393] TTI_time[1019,8,0] TTIslotIdx[20396]

[07-27 15:35:33.385][ERROR][DRV] FH_Rx, header[1019,7,1] SlotIdx[20395] TTI_time[1019,9,0] TTIslotIdx[20398]

[07-27 15:35:33.386][ERROR][DRV] FH_Rx, header[1019,8,1] SlotIdx[20397] TTI_time[1020,0,0] TTIslotIdx[20400]

[07-27 15:35:33.387][ERROR][DRV] FH_Rx, header[1019,9,1] SlotIdx[20399] TTI_time[1020,1,0] TTIslotIdx[20402]

[07-27 15:35:33.388][ERROR][DRV] FH_Rx, header[1020,0,1] SlotIdx[20401] TTI_time[1020,2,0] TTIslotIdx[20404]

[07-27 15:35:33.389][ERROR][DRV] FH_Rx, header[1020,1,1] SlotIdx[20403] TTI_time[1020,3,0] TTIslotIdx[20406]

[07-27 15:35:33.390][ERROR][DRV] FH_Rx, header[1020,2,1] SlotIdx[20405] TTI_time[1020,4,0] TTIslotIdx[20408]

[07-27 15:35:33.391][ERROR][DRV] FH_Rx, header[1020,3,1] SlotIdx[20407] TTI_time[1020,5,0] TTIslotIdx[20410]

[07-27 15:35:33.392][ERROR][DRV] FH_Rx, header[1020,4,1] SlotIdx[20409] TTI_time[1020,6,0] TTIslotIdx[20412]

[07-27 15:35:33.393][ERROR][DRV] FH_Rx, header[1020,5,1] SlotIdx[20411] TTI_time[1020,7,0] TTIslotIdx[20414]

[07-27 15:35:33.394][ERROR][DRV] FH_Rx, header[1020,6,1] SlotIdx[20413] TTI_time[1020,8,0] TTIslotIdx[20416]

[07-27 15:35:33.395][ERROR][DRV] FH_Rx, header[1020,7,1] SlotIdx[20415] TTI_time[1020,9,0] TTIslotIdx[20418]

[07-27 15:35:33.396][ERROR][DRV] FH_Rx, header[1020,8,1] SlotIdx[20417] TTI_time[1021,0,0] TTIslotIdx[20420]

[07-27 15:35:33.397][ERROR][DRV] FH_Rx, header[1020,9,1] SlotIdx[20419] TTI_time[1021,1,0] TTIslotIdx[20422]

[07-27 15:35:33.398][ERROR][DRV] FH_Rx, header[1021,0,1] SlotIdx[20421] TTI_time[1021,2,0] TTIslotIdx[20424]

[07-27 15:35:33.399][ERROR][DRV] FH_Rx, header[1021,1,1] SlotIdx[20423] TTI_time[1021,3,0] TTIslotIdx[20426]

[07-27 15:35:33.400][ERROR][DRV] FH_Rx, header[1021,2,1] SlotIdx[20425] TTI_time[1021,4,0] TTIslotIdx[20428]

[07-27 15:35:33.401][ERROR][DRV] FH_Rx, header[1021,3,1] SlotIdx[20427] TTI_time[1021,5,0] TTIslotIdx[20430]

[07-27 15:35:33.402][ERROR][DRV] FH_Rx, header[1021,4,1] SlotIdx[20429] TTI_time[1021,6,0] TTIslotIdx[20432]

[07-27 15:35:33.403][ERROR][DRV] FH_Rx, header[1021,5,1] SlotIdx[20431] TTI_time[1021,7,0] TTIslotIdx[20434]

[07-27 15:35:33.404][ERROR][DRV] FH_Rx, header[1021,6,1] SlotIdx[20433] TTI_time[1021,8,0] TTIslotIdx[20436]

[07-27 15:35:33.405][ERROR][DRV] FH_Rx, header[1021,7,1] SlotIdx[20435] TTI_time[1021,9,0] TTIslotIdx[20438]

[07-27 15:35:33.406][ERROR][DRV] FH_Rx, header[1021,8,1] SlotIdx[20437] TTI_time[1022,0,0] TTIslotIdx[20440]

[07-27 15:35:33.407][ERROR][DRV] FH_Rx, header[1021,9,1] SlotIdx[20439] TTI_time[1022,1,0] TTIslotIdx[20442]

[07-27 15:35:33.408][ERROR][DRV] FH_Rx, header[1022,0,1] SlotIdx[20441] TTI_time[1022,2,0] TTIslotIdx[20444]

[07-27 15:35:33.409][ERROR][DRV] FH_Rx, header[1022,1,1] SlotIdx[20443] TTI_time[1022,3,0] TTIslotIdx[20446]

[07-27 15:35:33.410][ERROR][DRV] FH_Rx, header[1022,2,1] SlotIdx[20445] TTI_time[1022,4,0] TTIslotIdx[20448]

[07-27 15:35:33.411][ERROR][DRV] FH_Rx, header[1022,3,1] SlotIdx[20447] TTI_time[1022,5,0] TTIslotIdx[20450]

[07-27 15:35:33.412][ERROR][DRV] FH_Rx, header[1022,4,1] SlotIdx[20449] TTI_time[1022,6,0] TTIslotIdx[20452]

[07-27 15:35:33.413][ERROR][DRV] FH_Rx, header[1022,5,1] SlotIdx[20451] TTI_time[1022,7,0] TTIslotIdx[20454]

[07-27 15:35:33.414][ERROR][DRV] FH_Rx, header[1022,6,1] SlotIdx[20453] TTI_time[1022,8,0] TTIslotIdx[20456]

[07-27 15:35:33.415][ERROR][DRV] FH_Rx, header[1022,7,1] SlotIdx[20455] TTI_time[1022,9,0] TTIslotIdx[20458]

[07-27 15:35:33.416][ERROR][DRV] FH_Rx, header[1022,8,1] SlotIdx[20457] TTI_time[1023,0,0] TTIslotIdx[20460]

[07-27 15:35:33.417][ERROR][DRV] FH_Rx, header[1022,9,1] SlotIdx[20459] TTI_time[1023,1,0] TTIslotIdx[20462]

[07-27 15:35:33.418][ERROR][DRV] FH_Rx, header[1023,0,1] SlotIdx[20461] TTI_time[1023,2,0] TTIslotIdx[20464]

[07-27 15:35:33.419][ERROR][DRV] FH_Rx, header[1023,1,1] SlotIdx[20463] TTI_time[1023,3,0] TTIslotIdx[20466]

[07-27 15:35:33.420][ERROR][DRV] FH_Rx, header[1023,2,1] SlotIdx[20465] TTI_time[1023,4,0] TTIslotIdx[20468]

[07-27 15:35:33.421][ERROR][DRV] FH_Rx, header[1023,3,1] SlotIdx[20467] TTI_time[1023,5,0] TTIslotIdx[20470]

[07-27 15:35:33.422][ERROR][DRV] FH_Rx, header[1023,4,1] SlotIdx[20469] TTI_time[1023,6,0] TTIslotIdx[20472]

[07-27 15:35:33.423][ERROR][DRV] FH_Rx, header[1023,5,1] SlotIdx[20471] TTI_time[1023,7,0] TTIslotIdx[20474]

[07-27 15:35:33.424][ERROR][DRV] FH_Rx, header[1023,6,1] SlotIdx[20473] TTI_time[1023,8,0] TTIslotIdx[20476]

由 匿名用户 更新于 超过 4 年 之前

出规避版本,前传数据获取地址从后面symbol 10 获取,不从0 获取了。

uint32_t dm_fh_rx_msg_parase(void *pFhRxBuf)

{

CpaBbBufferListStruct *pDestBuf = pFhRxBuf;

uint8_t *pChar;

FHHeaderStruct *psHeader;

uint32_t slot;

uint32_t pTimeInd = 0;

pChar = pDestBuf->pBuffers[10].pData; /* 规避错误,符号0-3的slot偶现跳变的现象 */

psHeader = (FHHeaderStruct *)pChar;

pTimeInd |= (psHeader->slotIdx & 0x1F);

pTimeInd |= (psHeader->subfIdx & 0x3F) << 5;

pTimeInd |= (psHeader->frameIdx & 0x3FF) << 11;

pTimeInd |= (psHeader->symIdx & 0x0F) << 21;

slot = psHeader->frameIdx*10*2 + psHeader->subfIdx*2 + psHeader->slotIdx;

if(g_zlogMask & ZLOG_DRIVER_DM)

{

zLog(PHY_LOG_TRACE,"FH_RX(%d,%d,%d), symIdx %d, slot %d, Len=%d\n",

psHeader->frameIdx, psHeader->subfIdx, psHeader->slotIdx, psHeader->symIdx, slot, psHeader->pktLen);

}

return pTimeInd;

}

另外增加异常保护,防止出现发送的descriptor地址错误;

if (lastdecriRec != 0)

{

if ((CurrentdecriRec > lastdecriRec) && ((CurrentdecriRec - lastdecriRec) != 0xF000))

{

zLog(PHY_LOG_ERROR, "Descriptors jump! symbol[%u]-->CurrentdecriRec[0x%08x], lastdecriRec[0x%08x]",

i, CurrentdecriRec, lastdecriRec);

}

else if ((CurrentdecriRec < lastdecriRec) && ((lastdecriRec - CurrentdecriRec) != 0x681000))

{

zLog(PHY_LOG_ERROR, "Descriptors jump! symbol[%u]-->CurrentdecriRec[0x%08x], lastdecriRec[0x%08x]",

i, CurrentdecriRec, lastdecriRec);

}

}

lastdecriRec = CurrentdecriRec;