错误 #592

大上行问题debug

0%

描述

现象:可以到随机接入,但是花费时间最长可以到17分钟

调试:

①fpga使用单音+频谱仪零span确认配比

②fpga确认接收功率

③其他再行讨论

文件

历史记录

由 匿名用户 更新于 超过 4 年 之前

- 文件 大上行0span观察.jpg 大上行0span观察.jpg 已添加

- 文件 大上行0span观察2.jpg 大上行0span观察2.jpg 已添加

- 状态 从 新建 变更为 进行中

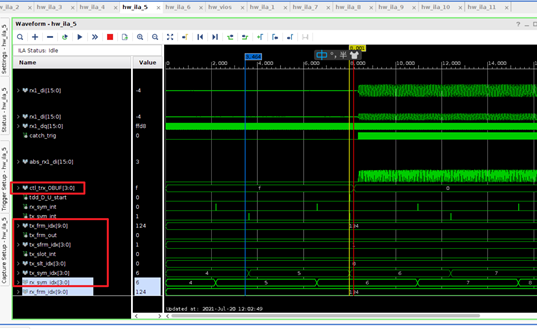

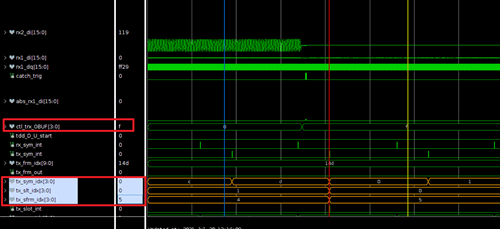

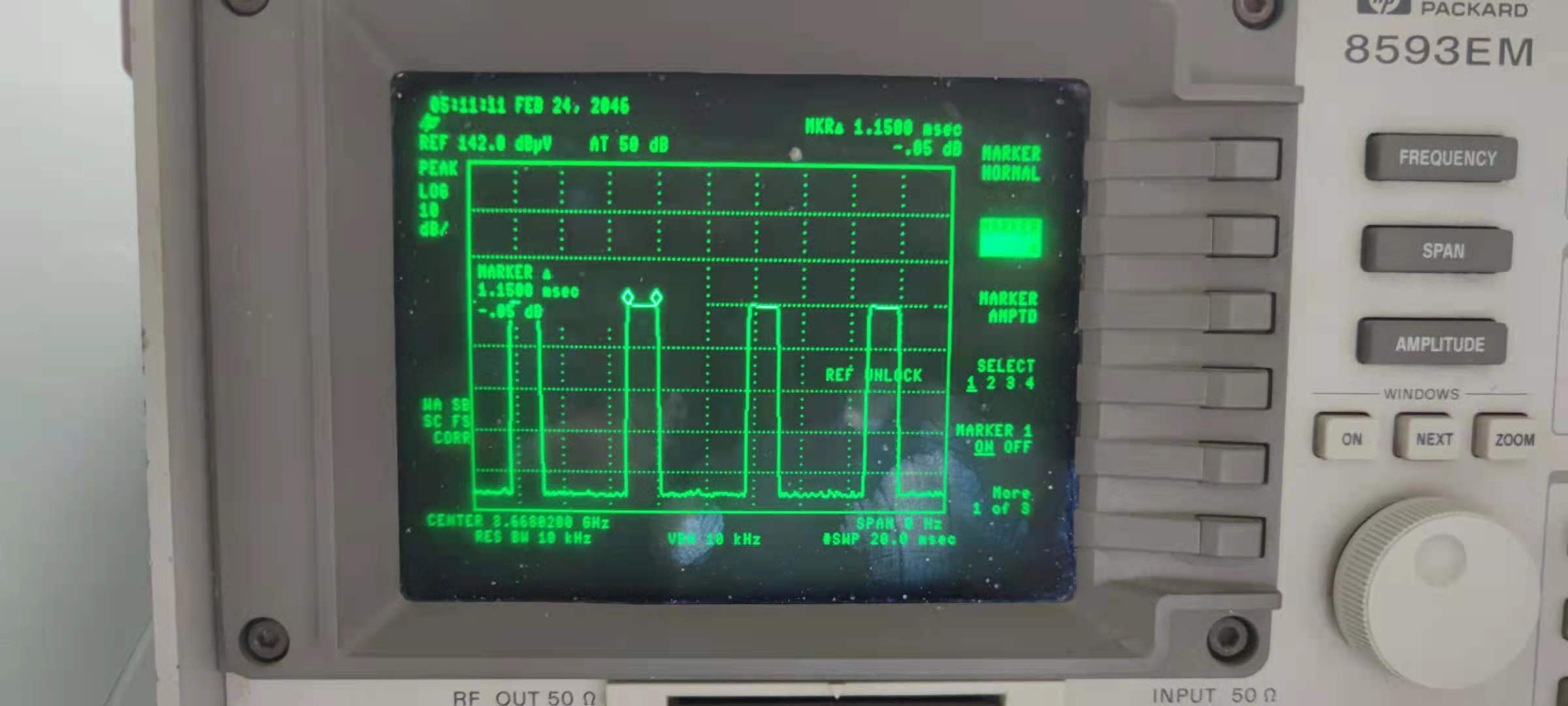

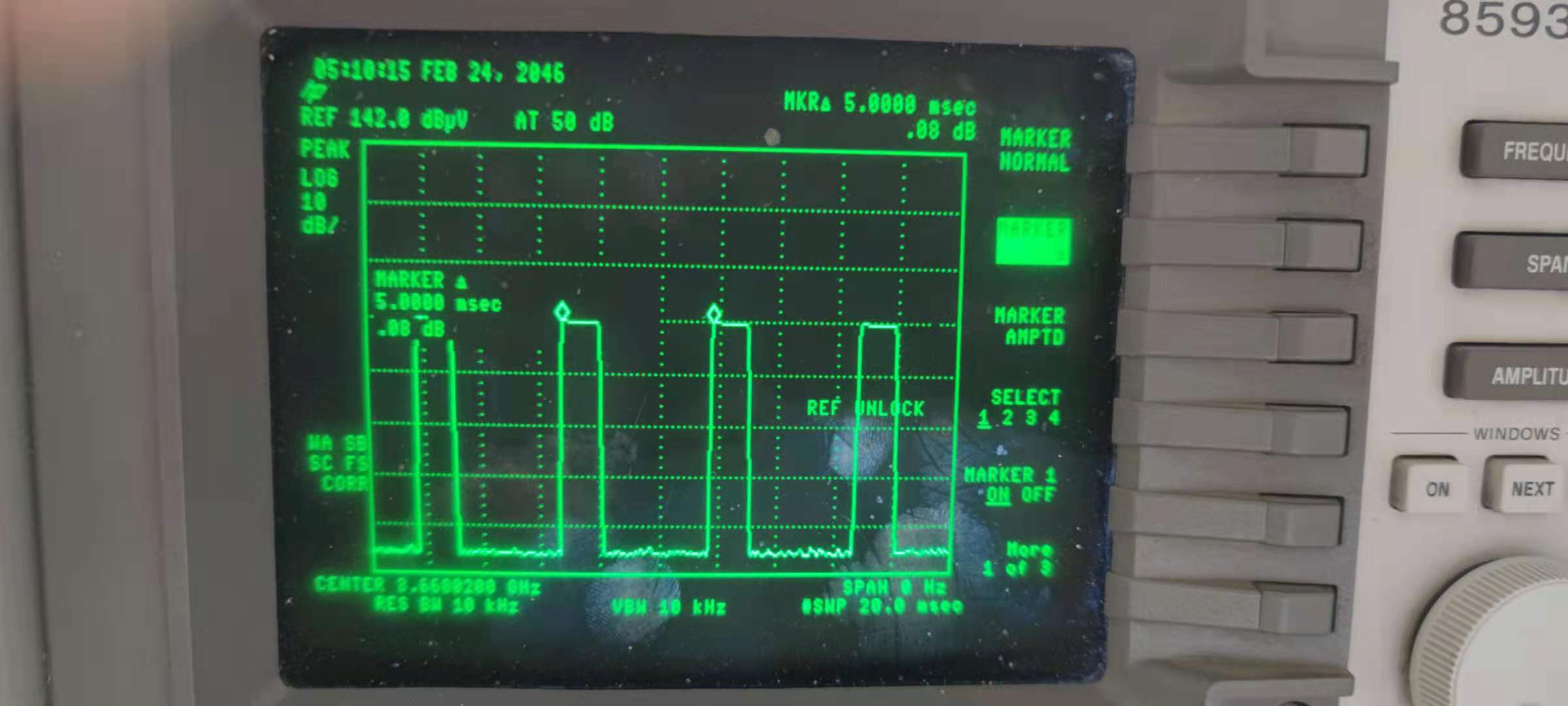

①fpga使用单音+频谱仪零span确认配比

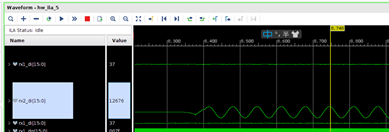

确认配比正常,切换时间计算,周期5ms=10slot,在第2slot切换。计算【下行】占时1ms+0.214ms ≈1.21ms,【上行】占时间=3.5+0.14ms+0.11ms≈3.75ms

见下图:图中周期5ms,下行占据1.15/1.20ms

②fpga确认接收功率

③其他再行讨论

由 匿名用户 更新于 超过 4 年 之前

- 文件 u-d切换位置.png u-d切换位置.png 已添加

- 文件 底噪.png 底噪.png 已添加

- 文件 d_u切换位置.png d_u切换位置.png 已添加

- 文件 天线0接收幅值.png 天线0接收幅值.png 已添加

- 文件 天线1接收幅值.png 天线1接收幅值.png 已添加

上行测试结果:

①天线0,接收功率符合之前记录。

实测幅值8650,实测输入功率-45dBm;根据记录幅值25500、功率-36.5dBm,推算输入功率-45.8dBm。

*****************************************************************************************************************

②天线1,接收功率大于天线0 约3dB

实测幅值12676,实测输入功率-45dBm,推算输入-42.5dBm

*****************************************************************************************************************

③底噪符合

测试幅值为100左右,记录值为115

*****************************************************************************************************************

④切换位置符合

d->u, u->d共四个位置, 上行表现符合大上行的位置