功能 #619

功能 #591: 转频电路上板测试

确认fpga内部计算结果

状态:

已解决

优先级:

一般

指派给:

-

类别:

FPGA

开始日期:

2021-08-06

计划完成日期:

% 完成:

100%

预期时间:

问题归属:

描述

观察sync_alg及调整的计算结果

文件

历史记录

由 匿名用户 更新于 超过 4 年 之前

- 文件 210820_负数问题.png 210820_负数问题.png 已添加

- 文件 210820-80msproc_发数样点稳定.png 210820-80msproc_发数样点稳定.png 已添加

- 文件 2021020-周期带来抖动.png 2021020-周期带来抖动.png 已添加

- 文件 20210820-复位问题.png 20210820-复位问题.png 已添加

- 文件 20210820-频偏峰值过小.png 20210820-频偏峰值过小.png 已添加

=============================================================================================================================================

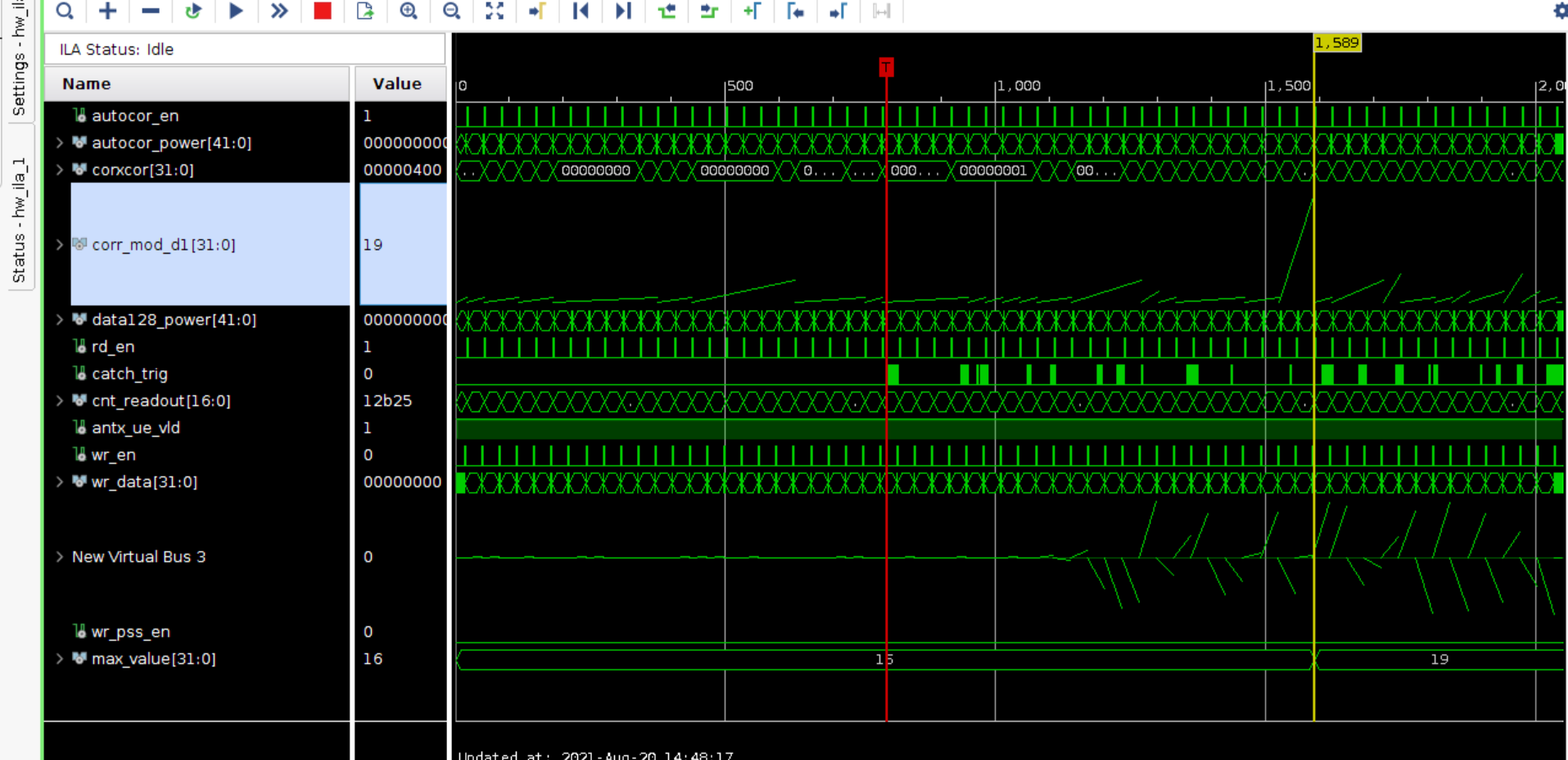

发数样点稳定

=============================================================================================================================================

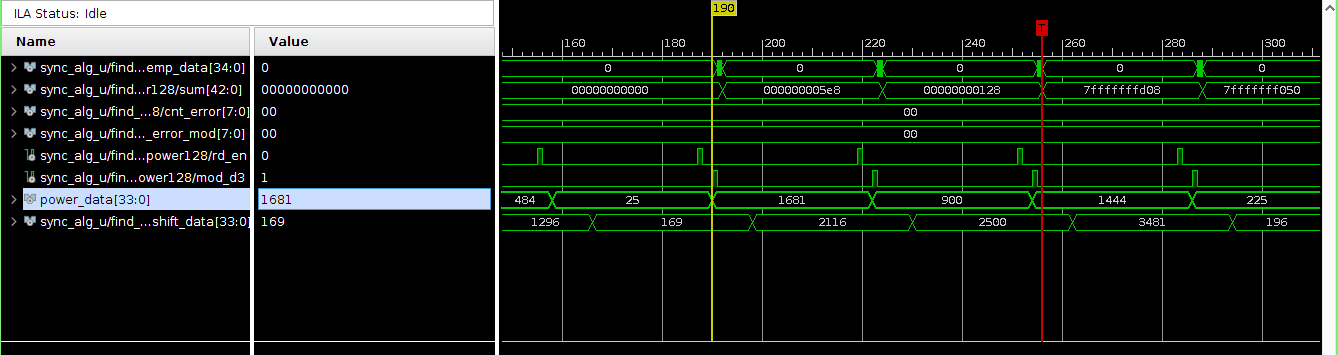

周期问题带来peak——pos抖动

=============================================================================================================================================

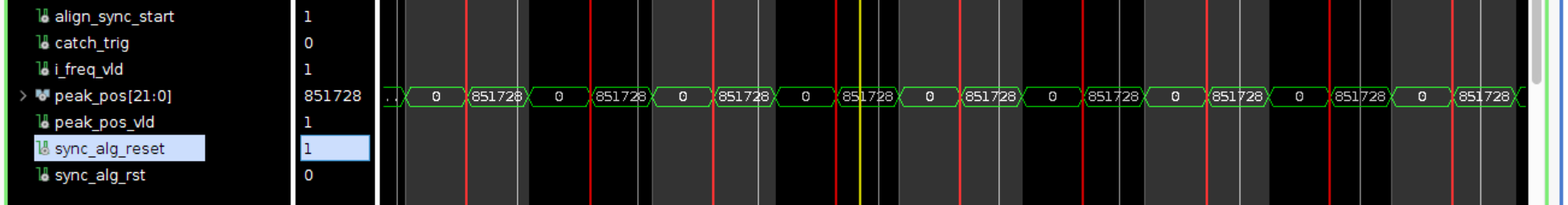

复位跟数据冲突问题

=============================================================================================================================================

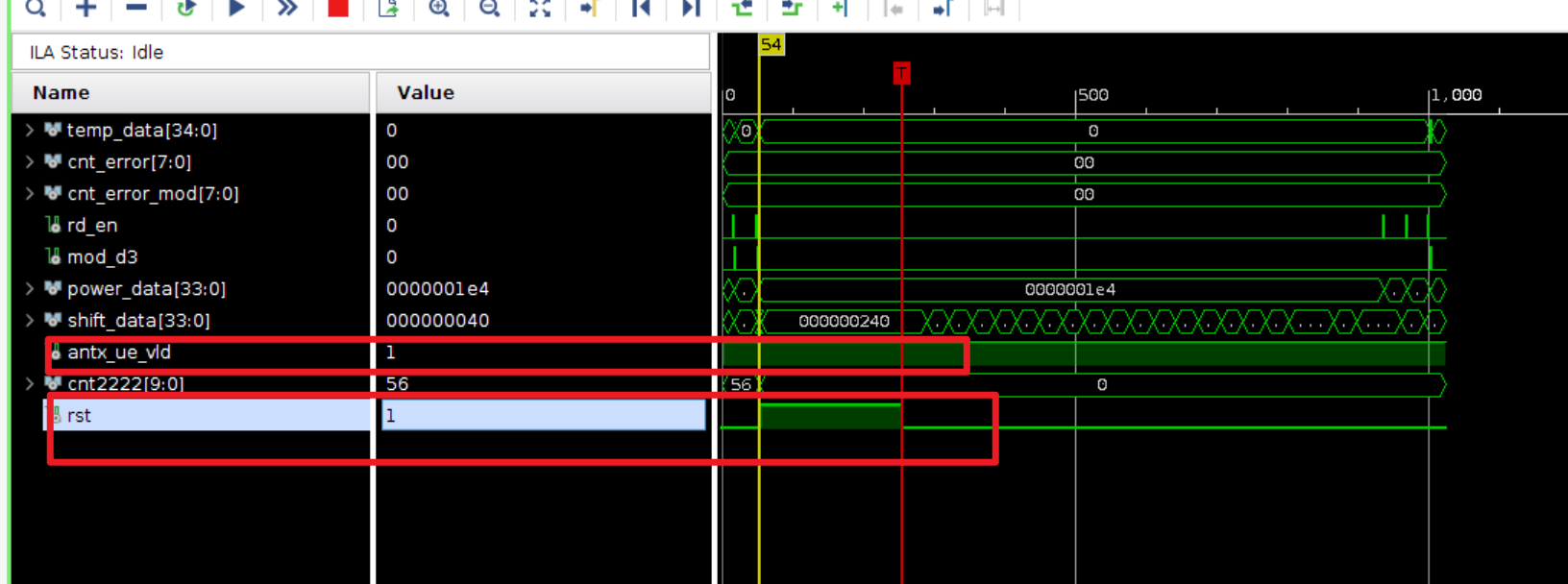

频偏导致峰值过小,信号未拉高