错误 #682

功能 #591: 转频电路上板测试

3.6/5.8的频率与理论不符 及 发转收高时延

状态:

已解决

优先级:

一般

指派给:

-

类别:

FPGA

开始日期:

2021-11-15

计划完成日期:

% 完成:

100%

预期时间:

(合计: 0.00 小时)

问题归属:

描述

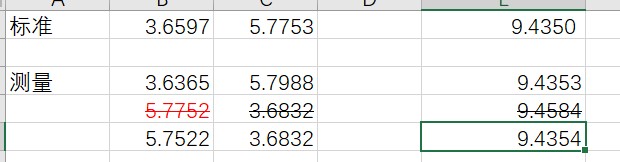

1.3.6G/5.8G频点的差值与理论不符

输入频点3.6365

输出频点5.7988

δ=2.1623

理论δ=5.7753-3.6597=2.1156

2.发射转接收 时延4800ns 过大

文件

子任务

历史记录

由 匿名用户 更新于 超过 4 年 之前

- 文件 211103_a.jpg 211103_a.jpg 已添加

- % 完成 从 0 变更为 50

1. 频率问题

①分析:

转频是高本振,所以freq(3.5G) + freq(5.8G)的和为固定,差不固定

②结果:

计算 和值 基本相同

差值是由于频谱仪固有的约150k频偏导致

2.发射转接收的高时延问题等待海泰反馈

由 匿名用户 更新于 超过 4 年 之前

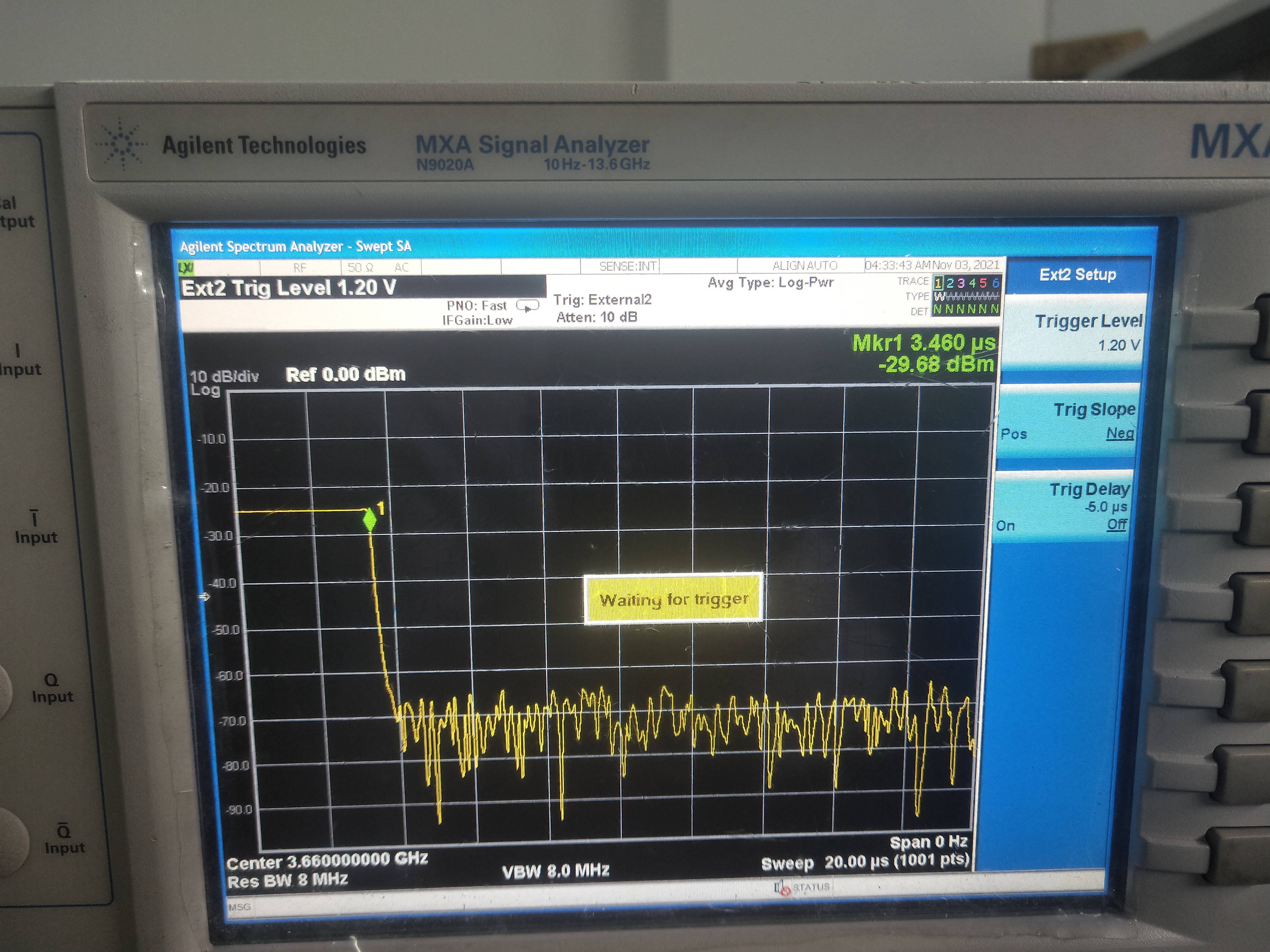

- 文件 211104_a.jpg 211104_a.jpg 已添加

发射转接收延迟,海泰反馈2us,其使用的频谱仪0span+触发

待后续转频工程使用频谱仪0span+触发验证

由 匿名用户 更新于 超过 4 年 之前

- 文件 211111.jpg 211111.jpg 已添加

trig测试

①R109电平,发射为高,接收为低,作为trig

②发射功率的增减作为信号

③观察trig到信号的时延