错误 #685

终端与基站首次同步存在22k~30k频偏

状态:

已解决

优先级:

高

指派给:

guo hanlin

开始日期:

2021-11-08

计划完成日期:

% 完成:

100%

预期时间:

问题归属:

CPU类型:

描述

2021.11.8

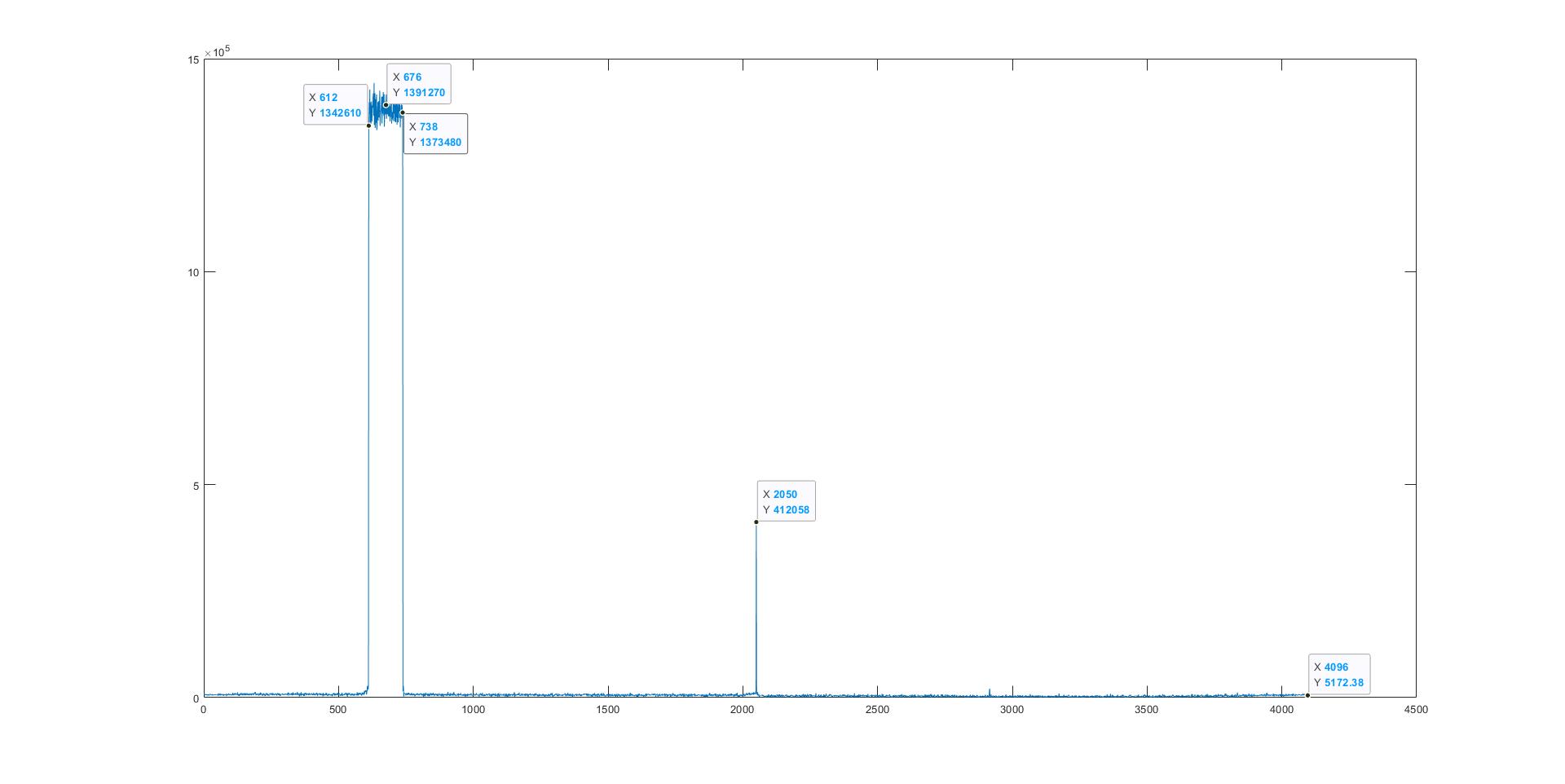

采数后matlab仿真发现,首次同步,每次都存在一个载波左右的频偏,范围在22k~30kHz左右

排除SSB配置错误导致的,原因是从9371出口采得一个时隙的时域数据,通过matlab画图发现中心直流信号存在偏移。

此问题涉及小区搜索调整方案的设计,需要通过FPGA发单音确认

2021.11.10

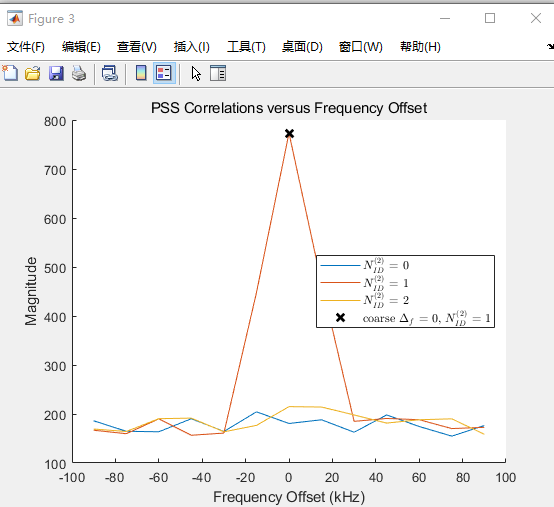

28kHz的大频偏是基站 +终端,双方的dac设置不当造成的,

频偏两部分组成 ①基站侧设置5683,值为0,偏移了大概13k,正确值应为32768附近;②终端侧,设置9371 auxdac, 值为698,偏移了剩余的大概15k,正确值应为320附近;

终端dac5683设置为32767(./MT barWrite $FPGA_CARD 600 VALUE),基站9371 auxdac设置为320(修改路径root/yzmm/rel/GNB/phy/drv/inc/rf9371.config.json)

问题解决,重新采数分析,频偏为585Hz, 符合预期

文件

历史记录

由 guo hanlin 更新于 超过 4 年 之前

由 guo hanlin 更新于 超过 4 年 之前

- 文件 飞书20211110-145559.png 飞书20211110-145559.png 已添加

- 描述 已更新。 (diff)

- 状态 从 新建 变更为 已解决

- % 完成 从 0 变更为 100